- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373080 > K7A801800B-QC16 (SAMSUNG SEMICONDUCTOR CO. LTD.) 256Kx36 & 512Kx18-Bit Synchronous Pipelined Burst SRAM PDF資料下載

參數(shù)資料

| 型號: | K7A801800B-QC16 |

| 廠商: | SAMSUNG SEMICONDUCTOR CO. LTD. |

| 英文描述: | 256Kx36 & 512Kx18-Bit Synchronous Pipelined Burst SRAM |

| 中文描述: | 256Kx36 |

| 文件頁數(shù): | 9/18頁 |

| 文件大小: | 400K |

| 代理商: | K7A801800B-QC16 |

K7A801809B

256Kx36 & 512Kx18 Synchronous SRAM

- 9 -

Rev 3.0

Nov. 2003

K7A803609B

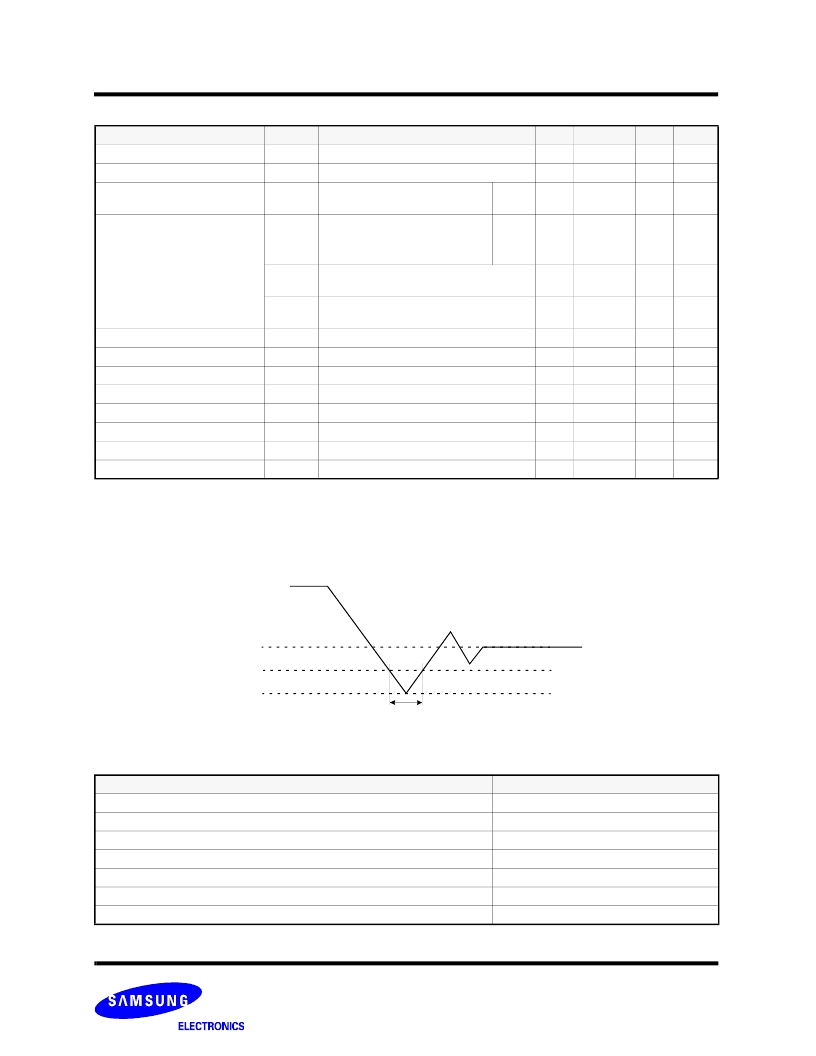

DC ELECTRICAL CHARACTERISTICS

(V

DD

=3.3V+0.165V/-0.165V, T

A

=0

°

C to +70

°

C)

Notes :

The above parameters are also guaranteed at industrial temperature range.

1. Reference AC Operating Conditions and Characteristics for input and timing.

2. Data states are all zero.

3. In Case of I/O Pins, the Max. V

IH

=V

DDQ

+0.3V.

PARAMETER

SYMBOL

TEST CONDITIONS

MIN

MAX

UNIT

NOTES

Input Leakage Current(except ZZ)

I

IL

V

DD

= Max ; V

IN

=V

SS

to V

DD

-2

+2

μ

A

Output Leakage Current

I

OL

Output Disabled, V

OUT

=V

SS

to V

DDQ

-2

+2

μ

A

Operating Current

I

CC

Device Selected, I

OUT

=0mA,

ZZ

≤

V

IL ,

Cycle Time

≥

t

CYC

Min

-25

-

470

mA

1,2

Standby Current

I

SB

Device deselected, I

OUT

=0mA,

ZZ

≤

V

IL

, f=Max,

All Inputs

≤

0.2V or

≥

V

DD

-0.2V

-25

-

170

mA

I

SB1

Device deselected, I

OUT

=0mA, ZZ

≤

0.2V,

f = 0, All Inputs=fixed (V

DD

-0.2V or 0.2V)

-

100

mA

I

SB2

Device deselected, I

OUT

=0mA, ZZ

≥

V

DD

-0.2V,

f=Max, All Inputs

≤

V

IL

or

≥

V

IH

-

60

mA

Output Low Voltage(3.3V I/O)

V

OL

I

OL

=8.0mA

-

0.4

V

Output High Voltage(3.3V I/O)

V

OH

I

OH

=-4.0mA

2.4

-

V

Output Low Voltage(2.5V I/O)

V

OL

I

OL

=1.0mA

-

0.4

V

Output High Voltage(2.5V I/O)

V

OH

I

OH

=-1.0mA

2.0

-

V

Input Low Voltage(3.3V I/O)

V

IL

-0.3*

0.8

V

Input High Voltage(3.3V I/O)

V

IH

2.0

V

DD

+0.3

V

3

Input Low Voltage(2.5V I/O)

V

IL

-0.3*

0.7

V

Input High Voltage(2.5V I/O)

V

IH

1.7

V

DD

+0.3

V

3

V

SS

V

IH

V

SS-

1.0V

20% t

CYC

(MIN)

(V

DD

=3.3V+0.165V/-0.165V,V

DDQ

=3.3V+0.165/-0.165V or V

DD

=3.3V+0.165V/-0.165V,V

DDQ

=2.5V+0.4V/-0.125V, T

A

=0to70

°

C)

TEST CONDITIONS

* The above parameters are also guaranteed at industrial temperature range.

Parameter

Value

Input Pulse Level(for 3.3V I/O)

0 to 3.0V

Input Pulse Level(for 2.5V I/O)

0 to 2.5V

Input Rise and Fall Time(Measured at 20% to 80% for 3.3V I/O)

1.0V/ns

Input Rise and Fall Time(Measured at 20% to 80% for 2.5V I/O)

1.0V/ns

Input and Output Timing Reference Levels for 3.3V I/O

1.5V

Input and Output Timing Reference Levels for 2.5V I/O

V

DDQ

/2

Output Load

See Fig. 1

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| K7A801809B-QC25 | 256Kx36 & 512Kx18-Bit Synchronous Pipelined Burst SRAM |

| K7A801809B-QCI25 | 256Kx36 & 512Kx18-Bit Synchronous Pipelined Burst SRAM |

| K7B801825B-QC65 | 256Kx36 & 512Kx18-Bit Synchronous Pipelined Burst SRAM |

| K7B801825B-QC75 | 256Kx36 & 512Kx18-Bit Synchronous Pipelined Burst SRAM |

| K7B803625B-QC65 | 256Kx36 & 512Kx18-Bit Synchronous Pipelined Burst SRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| K7A801800M | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:256Kx36 & 512Kx18 Synchronous SRAM |

| K7A801801M | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:256Kx36 & 512Kx18 Synchronous SRAM |

| K7A801809A | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:256Kx36 & 512Kx18 Synchronous SRAM |

| K7A801809B | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:256Kx36 & 512Kx18-Bit Synchronous Pipelined Burst SRAM |

| K7A801809B-QC25 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:256Kx36 & 512Kx18-Bit Synchronous Pipelined Burst SRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。