- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373157 > KM48C8004B (SAMSUNG SEMICONDUCTOR CO. LTD.) 8M x 8bit CMOS Dynamic RAM with Extended Data Out PDF資料下載

參數(shù)資料

| 型號(hào): | KM48C8004B |

| 廠商: | SAMSUNG SEMICONDUCTOR CO. LTD. |

| 英文描述: | 8M x 8bit CMOS Dynamic RAM with Extended Data Out |

| 中文描述: | 8米× 8位的CMOS動(dòng)態(tài)隨機(jī)存儲(chǔ)器的擴(kuò)展數(shù)據(jù)輸出 |

| 文件頁數(shù): | 5/21頁 |

| 文件大?。?/td> | 383K |

| 代理商: | KM48C8004B |

KM48C8004B,

KM48C8104B

CMOS DRAM

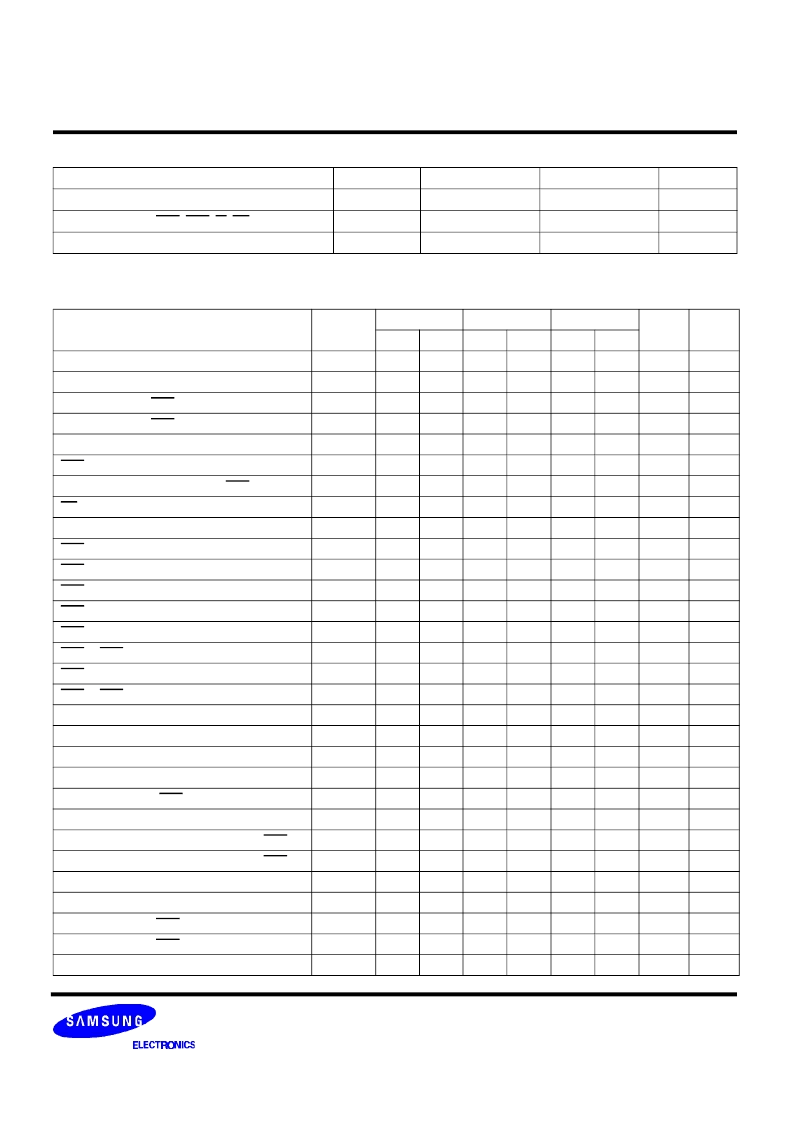

CAPACITANCE

(T

A

=25

°

C, V

CC

=5.0V, f=1MHz)

Parameter

Symbol

Min

Max

Units

Input capacitance [A0 ~ A12]

C

IN1

-

5

pF

Input capacitance [RAS, CAS, W, OE]

C

IN2

-

7

pF

Output capacitance [DQ0 - DQ7]

C

DQ

-

7

pF

Test condition : V

CC

=5.0V

±

10%, Vih/Vil=2.4/0.8V, Voh/Vol=2.0/0.8V

Parameter

Symbol

-45

-5

-6

Units

Note

Min

Max

Min

Max

Min

Max

Random read or write cycle time

t

RC

t

RWC

t

RAC

t

CAC

t

AA

t

CLZ

t

CEZ

t

OLZ

t

T

t

RP

74

84

104

ns

Read-modify-write cycle time

101

113

138

ns

Access time from RAS

45

50

60

ns

3,4,10

Access time from CAS

12

13

15

ns

3,4,5

Access time from column address

23

25

30

ns

3,10

CAS to output in Low-Z

3

3

3

ns

3

Output buffer turn-off delay from CAS

3

13

3

13

3

13

ns

6,14

OE to output in Low-Z

3

3

3

ns

3

Transition time (rise and fall)

1

50

1

50

1

50

ns

2

RAS precharge time

25

30

40

ns

RAS pulse width

t

RAS

t

RSH

t

CSH

t

CAS

t

RCD

t

RAD

t

CRP

t

ASR

t

RAH

t

ASC

t

CAH

t

RAL

45

10K

50

10K

60

10K

ns

RAS hold time

8

8

10

ns

CAS hold time

35

38

40

ns

CAS pulse width

7

5K

8

10K

10

10K

ns

RAS to CAS delay time

11

33

11

37

14

45

ns

4

RAS to column address delay time

9

22

9

25

12

30

ns

10

CAS to RAS precharge time

5

5

5

ns

Row address set-up time

0

0

0

ns

Row address hold time

7

7

10

ns

Column address set-up time

0

0

0

ns

Column address hold time

7

7

10

ns

Column address to RAS lead time

23

25

30

ns

Read command set-up time

t

RCS

t

RCH

t

RRH

t

WCH

t

WP

t

RWL

t

CWL

t

DS

0

0

0

ns

8

Read command hold time referenced to CAS

0

0

0

ns

8

Read command hold time referenced to RAS

0

0

0

ns

Write command hold time

7

7

10

ns

Write command pulse width

6

7

10

ns

Write command to RAS lead time

8

8

10

ns

Write command to CAS lead time

7

7

10

ns

Data set-up time

0

0

0

ns

9

AC CHARACTERISTICS

(0

°

C

≤

T

A

≤

70

°

C, See note 1,2)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| KM48L16031BT-G(L)Y | DDR SDRAM Specification Version 1.0 |

| KM416L8031BT-G(L)Y | DDR SDRAM Specification Version 1.0 |

| KM44L32031BT-G(L)Z | DDR SDRAM Specification Version 1.0 |

| KM48L16031BT-G(L)Z | DDR SDRAM Specification Version 1.0 |

| KM416L8031BT-G(L)Z | DDR SDRAM Specification Version 1.0 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| KM48C8100AS-60 | 制造商:Samsung Semiconductor 功能描述: |

| KM48C8104B | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:8M x 8bit CMOS Dynamic RAM with Extended Data Out |

| KM-48F 50UA DC | 制造商:Fujita Electric 功能描述: |

| KM-48F 0-50MV DC | 制造商:Fujita Electric 功能描述: |

| KM-48F 100-0-100UA DC | 制造商:Fujita Electric 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。