- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄30716 > LA3401 AM/FM, AUDIO DEMODULATOR, PDIP22 PDF資料下載

參數(shù)資料

| 型號: | LA3401 |

| 元件分類: | 接收器 |

| 英文描述: | AM/FM, AUDIO DEMODULATOR, PDIP22 |

| 封裝: | SDIP-22 |

| 文件頁數(shù): | 3/15頁 |

| 文件大小: | 467K |

| 代理商: | LA3401 |

LA3401

No.1868-13/17

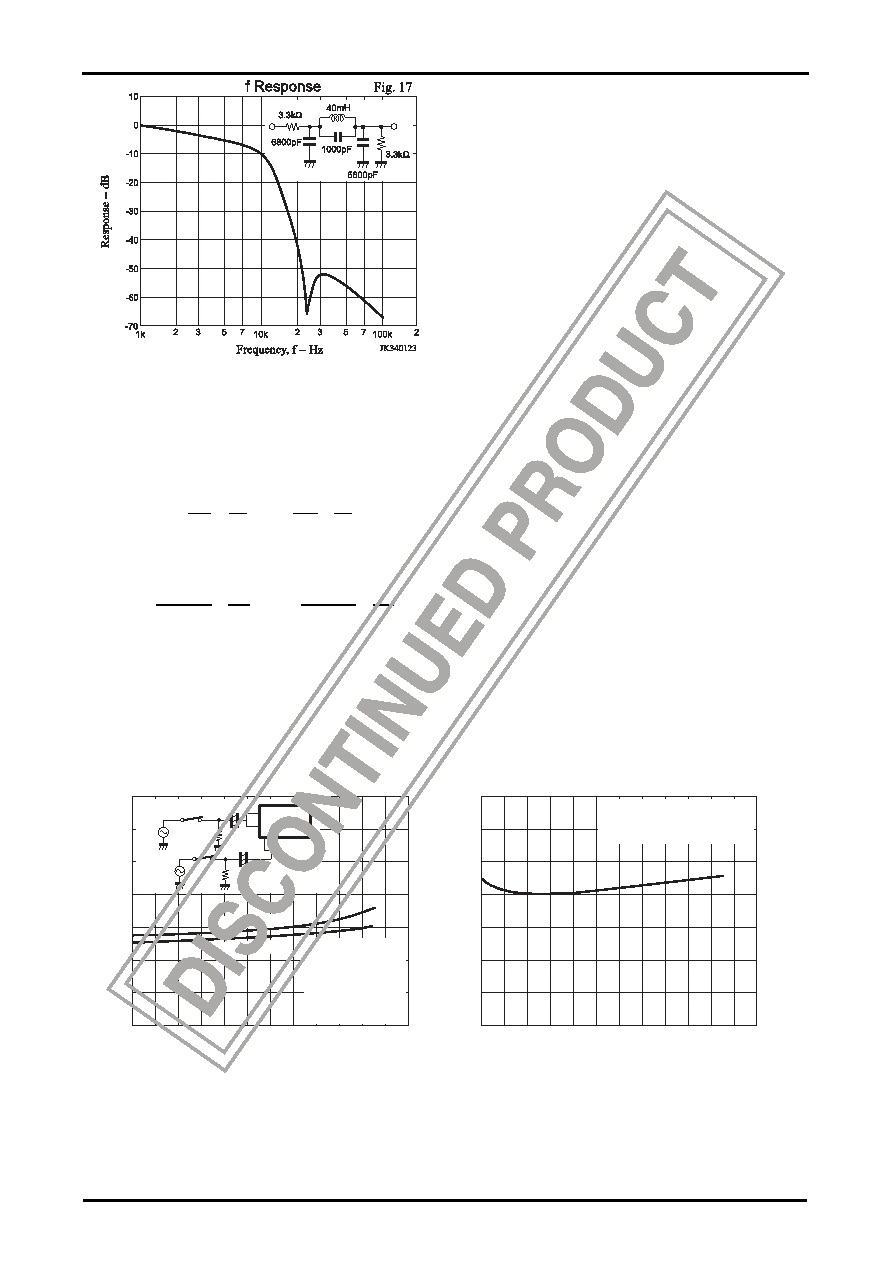

Decoder circuit (Refer to the Block Diagram in the Sample Application Circuit.)

The LA3401 adopts a decoder circuit of chopper type. The sub signal sync detected by this decoder is applied to the

post amplifier minus input through Rb as shown in the Sample Application Circuit. This signal is matrixed with the

main signal coming out of amplifier A5 and passing through RC.

The gain for the sub signal is :

R1

2

R2

2

VS

Rb

π

or VS

Rb

π

The gain for the main signal is :

VR1

R1

VR1

R2

VM

Ra+VR1

Rc

or VM

Ra+VR1

Rc

R1, R2 : Post amplifier feedback resistor

VS :

Peak value of input sub signal

VR1 :

Semifixed resistor for separation adjust

VM :

Peak value of input main signal

In the LA3401, the gain of the main signal is varied with VR1 to adjust the separation. Since the IF output is generally

such that the sub signal level is lower than the main signal level, the separation can be adjusted by attenuating the main

signal level with VR1. The use of an ant ibirdie filter across the IF output and the FM input of the LA3401 may cause

the sub signal level to be raised, and when the sub signal level is higher than the main signal level the separation cannot

be adjusted with VR1. In this case, the sub signal level is attenuated to be less than the main signal level and applied to

the LA3401 and the separation is adjusted with VR1.

16

75

76

82

Muting Attenuation -- VCC

Supply Voltage, VCC -- V

Muting

Attenuation

--

dB

JK340125

468

10

12

14

77

78

79

80

81

VIN = 400mV (AM, FM input)

No external muting

f = 1kHz

Fig. 19

16

69

70

76

Cross Talk -- VCC

Supply Voltage, VCC -- V

Crosstalk

-

-dB

JK340124

468

10

12

14

71

72

73

74

75

AM

FM

AM

Fig. 18

SG1

SG2

5.1k

Ω

5.1k

Ω

10

μF

10

μF

LA3401

2

1

f = 1kHz

VIN = 400mV

Pin 10 voltage 5V

5.1k

Ω termination

connected to SG

output (See left.)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LA3410 | FM, AUDIO DEMODULATOR, PDIP16 |

| LA3430M | FM, AUDIO DEMODULATOR, PDSO16 |

| LA3430 | FM, AUDIO DEMODULATOR, PZIP16 |

| LA3433 | FM, AUDIO DEMODULATOR, PDIP16 |

| LA3460M | SPECIALTY CONSUMER CIRCUIT, PDSO24 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LA3410 | 制造商:SANYO 制造商全稱:Sanyo Semicon Device 功能描述:VCO Non-Adjusting PLL FM MPX Stereo Demodulator with FM Accessories |

| LA3420 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述: |

| LA343 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Optoelectronic |

| LA3430 | 制造商:Panasonic Industrial Company 功能描述:IC |

| LA3430M | 制造商:SANYO 制造商全稱:Sanyo Semicon Device 功能描述:PLL FM MPX Stereo Demodulator with Pilot Canceler For Car Stereo Use |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。