- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄30723 > LA7477W SPECIALTY CONSUMER CIRCUIT, PQFP48 PDF資料下載

參數(shù)資料

| 型號(hào): | LA7477W |

| 元件分類: | 消費(fèi)家電 |

| 英文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP48 |

| 封裝: | 7 X 7 MM, SQFP-48 |

| 文件頁(yè)數(shù): | 9/12頁(yè) |

| 文件大小: | 129K |

| 代理商: | LA7477W |

LA7477W

No.5775-6/12

Serial Communications

Serial data

Parameter

Initial values

Bit 1

EVR CTL 1

L : 0, H : 1

0

Bit 2

EVR CTL 2

L : 0, H : 1

0

Bit 3

EVR CTL 3

L : 0, H : 1

0

Bit 4

EVR CTL 4

L : 0, H : 1

0

Bit 5

EVR CTL 5

L : 0, H : 1

0

Bit 6

Headphone and speaker

ON : 0, OFF : 1

1

Bit 7

EVR SERIAL

ON : 0, OFF : 1

1

Bit 8

12dB amplifier through state

OFF : 0, ON : 1

1

Bit 9

REC EVR SW

OFF : 0, ON : 1

0

Bit 10

DE-EMPH

OFF : 0, ON : 1

0

Bit 11

CONT1 OUT

L : 0, H : 1

1

Bit 12

CONT2 OUT

L : 0, H : 1

1

Bit 13

CONT3 OUT

L : 0, H : 1

1

Bit 14

CONT4 OUT

L : 0, H : 1

1

Bit 15

RFU SW

OFF : 0, ON : 1

0

Bit 16

STEREO/MAIN/SUB

STEREO : 0, MAIN : 0, SUB : 1

0

Bit 17

STEREO : 0, MAIN : 1, SUB : 0

0

Bit 18

ALC SW

ON : 0, OFF : 1

0

Bit 19

LINE OUT

ON : 0, OFF : 1

0

Bit 20

MIC/LINE1/LINE2/SPEAKER OFF

MIC : 0, LINE1 : 0, LINE2 : 1, SPEAKER OFF : 1

0

Bit 21

MIC : 0, LINE1 : 1, LINE2 : 0, SPEAKER OFF : 1

0

Bit 22

MUTE SW

OFF : 0, ON : 1

1

Bit 23

REC/PB/EE/POWER SAVE

REC : 0, PB : 0, EE : 1, POWER SAVE : 1

0

Bit 24

REC : 0, PB : 1, EE : 0, POWER SAVE : 1

0

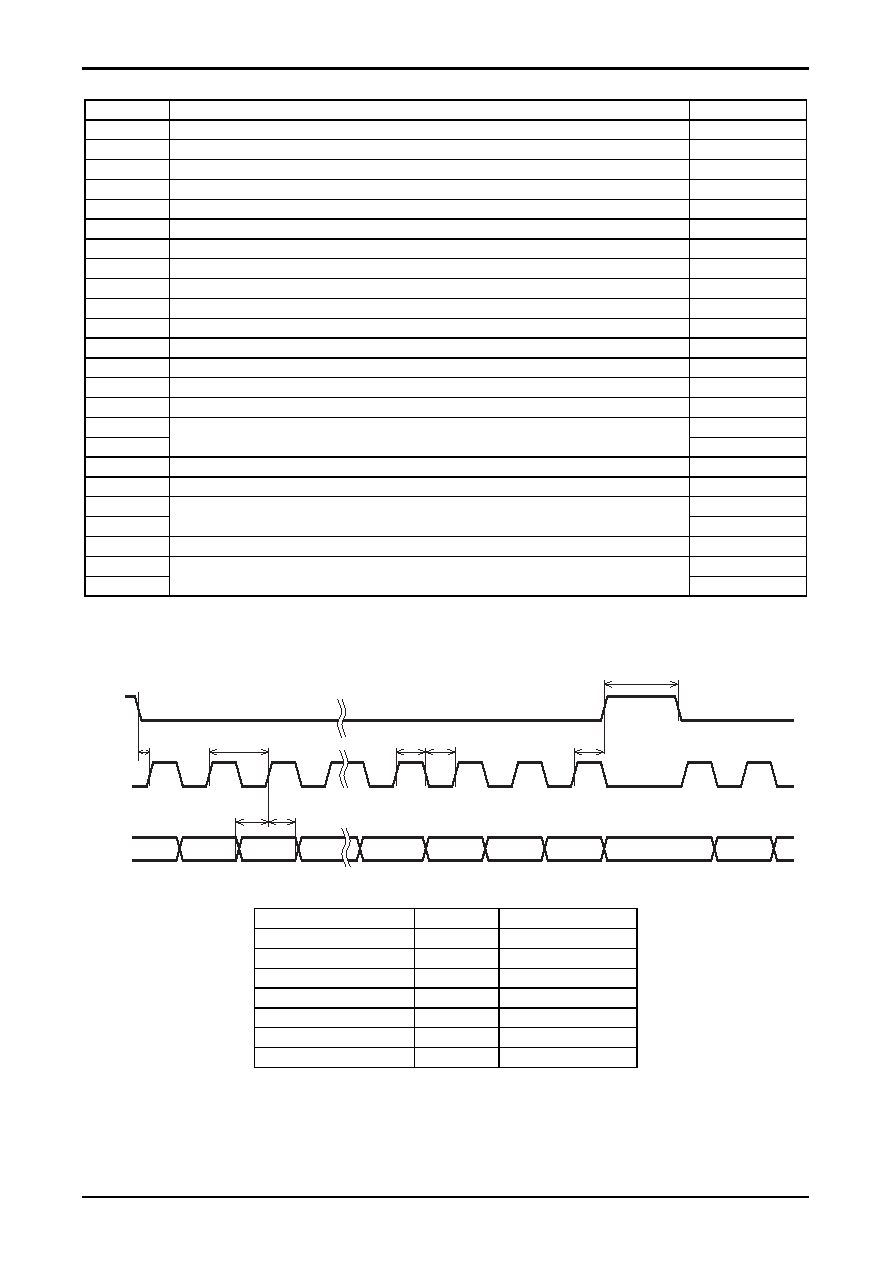

Serial Transfer Timing

Maximum clock frequency

fMAX

800kHz

Clock pulse width (low)

tWL

625ns minimum

Clock pulse width (high)

tWH

625ns minimum

Chip enable setup time

tCS

625ns minimum

Chip enable hold time

tCH

625ns minimum

Data setup tim

tDS

625ns minimum

Data hold time

tDH

625ns minimum

Chip enable pulse width

tWC

625ns minimum

fMAX

tCS

tDS tDH

tWH tWL

tCH

MSB

LSB

tWC

CS

CLOCK

DATA

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LA7477W | SPECIALTY CONSUMER CIRCUIT, PQFP48 |

| LA7510 | SPECIALTY CONSUMER CIRCUIT, PSIP9 |

| LA7520N | AM/FM, AUDIO/VIDEO DEMODULATOR, PDIP30 |

| LA7521 | AM/FM, AUDIO/VIDEO DEMODULATOR, PDIP30 |

| LA7520 | AM/FM, AUDIO/VIDEO DEMODULATOR, PDIP30 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LA7505 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述: |

| LA7506 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Analog IC |

| LA7507 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Analog IC |

| LA7508 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Analog IC |

| LA7509 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。