- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377611 > LC5512MC-45F484C (LATTICE SEMICONDUCTOR CORP) 3.3V, 2.5V and 1.8V In-System Programmable eXpanded Programmable Logic Device XPLD⑩ Family PDF資料下載

參數(shù)資料

| 型號(hào): | LC5512MC-45F484C |

| 廠商: | LATTICE SEMICONDUCTOR CORP |

| 元件分類: | PLD |

| 英文描述: | 3.3V, 2.5V and 1.8V In-System Programmable eXpanded Programmable Logic Device XPLD⑩ Family |

| 中文描述: | EE PLD, 5.7 ns, PBGA484 |

| 封裝: | FPBGA-484 |

| 文件頁(yè)數(shù): | 39/92頁(yè) |

| 文件大小: | 378K |

| 代理商: | LC5512MC-45F484C |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)當(dāng)前第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)

Lattice Semiconductor

ispXPLD 5000MX Family Data Sheet

39

t

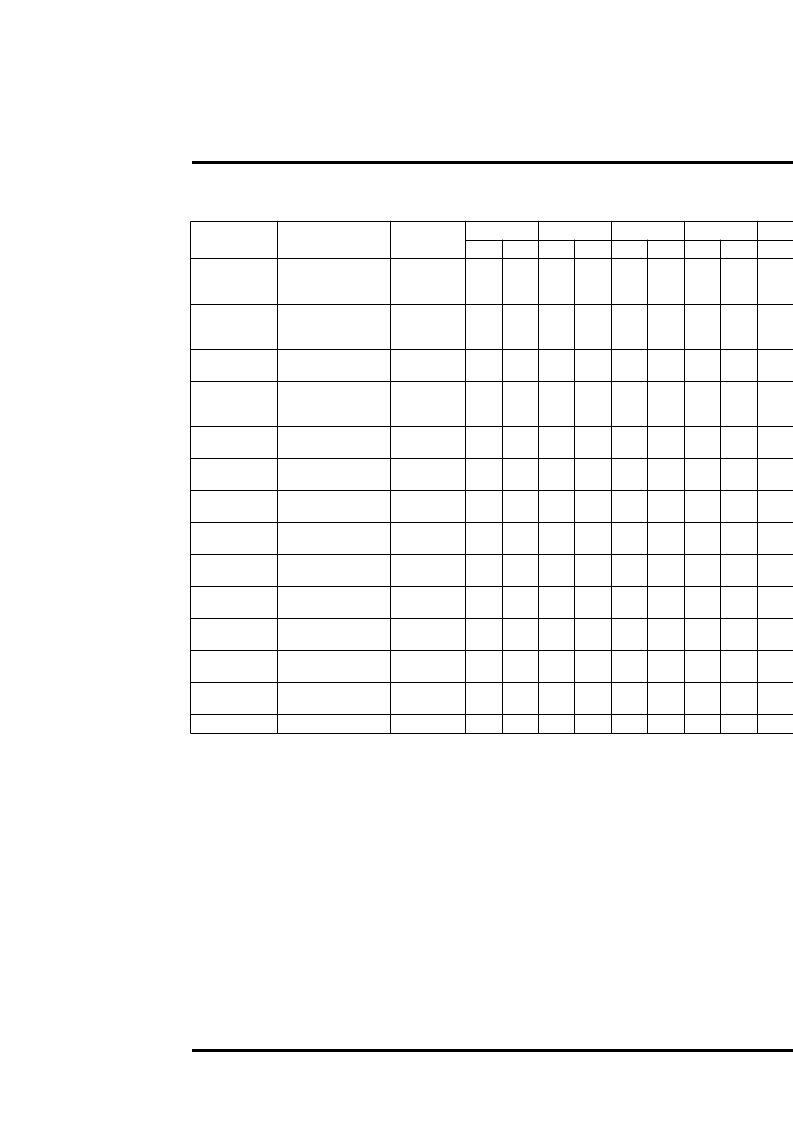

DPCEBS

Clock Enable B

Setup before Clock

B Time

Clock Enable Hold

B after Clock B

Time

Address B Setup

before Clock B Time

Address B Hold

time after Clock B

Time

R/W B Setup before

Clock B Time

R/W B Hold time

after Clock B Time

Write Data B Setup

before Clock B Time

Write Data B Hold

after Clock B Time

Read Clock A to

Output Delay

Read Clock B to

Output Delay

Opposite Clock

Cycle Delay

Reset to RAM

Output Delay

Reset Recovery

Time

Reset Pulse Width

—

2.33

—

2.33

—

2.33

—

2.33

—

3.03

—

ns

t

DPCEBH

—

-2.95

—

-2.95

—

-2.95

—

-2.95

—

-2.27

—

ns

t

DPADDBS

—

-0.27

—

-0.27

—

-0.27

—

-0.27

—

-0.21

—

ns

t

DPADDBH

—

-0.01

—

-0.01

—

-0.01

—

-0.01

—

-0.01

—

ns

t

DPRWBS

—

-0.27

—

-0.27

—

-0.27

—

-0.27

—

-0.21

—

ns

t

DPRWBH

—

-0.01

—

-0.01

—

-0.01

—

-0.01

—

-0.01

—

ns

t

DPDATABS

—

-0.27

—

-0.27

—

-0.27

—

-0.27

—

-0.21

—

ns

t

DPDATABH

—

-0.01

—

-0.01

—

-0.01

—

-0.01

—

-0.01

—

ns

t

DPRCLKAO

—

—

5.97

—

5.92

—

5.86

—

5.65

—

9.86

ns

t

DPRCLKBO

—

—

5.16

—

5.16

—

5.16

—

5.16

—

6.71

ns

t

DPCLKSKEW

—

1.40

—

1.40

—

1.40

—

1.40

—

1.83

—

ns

t

DPRSTO

—

—

3.30

—

3.30

—

3.30

—

3.30

—

4.29

ns

t

DPRSTR

—

1.20

—

1.20

—

1.20

—

1.20

—

1.56

—

ns

t

DPRSTPW

—

0.14

—

0.14

—

0.14

—

0.14

—

0.19

—

ns

1. The PT-delay to clock of RAM/FIFO/CAM should be t

BCLK

instead of t

PTCLK.

2. The PT-delay to set/reset of RAM/FIFO/CAM should be t

BSR

instead of t

PTSR.

ispXPLD 5000MX Family Internal Switching Characteristics (Continued)

Over Recommended Operating Conditions

Parameter

Description

Base

Parameter

-4

-45

-5

-52

-75

Units

Min.

Max.

Min.

Max.

Min.

Max.

Min.

Max.

Min.

Max.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LC5512MC-45Q208C | 3.3V, 2.5V and 1.8V In-System Programmable eXpanded Programmable Logic Device XPLD⑩ Family |

| LC5512MC-75F256C | 3.3V, 2.5V and 1.8V In-System Programmable eXpanded Programmable Logic Device XPLD⑩ Family |

| LC5512MC-75F484C | 3.3V, 2.5V and 1.8V In-System Programmable eXpanded Programmable Logic Device XPLD⑩ Family |

| LC5512MC-75Q208C | 3.3V, 2.5V and 1.8V In-System Programmable eXpanded Programmable Logic Device XPLD⑩ Family |

| LC5768MC-5F256C | 3.3V, 2.5V and 1.8V In-System Programmable eXpanded Programmable Logic Device XPLD⑩ Family |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LC5512MC-45F484I | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:3.3V, 2.5V and 1.8V In-System Programmable eXpanded Programmable Logic Device XPLD⑩ Family |

| LC5512MC-45F672C | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:3.3V, 2.5V and 1.8V In-System Programmable eXpanded Programmable Logic Device XPLD⑩ Family |

| LC5512MC-45F672I | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:3.3V, 2.5V and 1.8V In-System Programmable eXpanded Programmable Logic Device XPLD⑩ Family |

| LC5512MC-45FN208C | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:3.3V, 2.5V and 1.8V In-System Programmable eXpanded Programmable Logic Device XPLD⑩ Family |

| LC5512MC-45FN208I | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:3.3V, 2.5V and 1.8V In-System Programmable eXpanded Programmable Logic Device XPLD⑩ Family |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。