- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377611 > LC5512MC-75Q208C (LATTICE SEMICONDUCTOR CORP) 3.3V, 2.5V and 1.8V In-System Programmable eXpanded Programmable Logic Device XPLD⑩ Family PDF資料下載

參數(shù)資料

| 型號: | LC5512MC-75Q208C |

| 廠商: | LATTICE SEMICONDUCTOR CORP |

| 元件分類: | PLD |

| 英文描述: | 3.3V, 2.5V and 1.8V In-System Programmable eXpanded Programmable Logic Device XPLD⑩ Family |

| 中文描述: | EE PLD, 9.5 ns, PQFP208 |

| 封裝: | PLASTIC, QFP-208 |

| 文件頁數(shù): | 18/92頁 |

| 文件大小: | 378K |

| 代理商: | LC5512MC-75Q208C |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁當(dāng)前第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁

Lattice Semiconductor

ispXPLD 5000MX Family Data Sheet

18

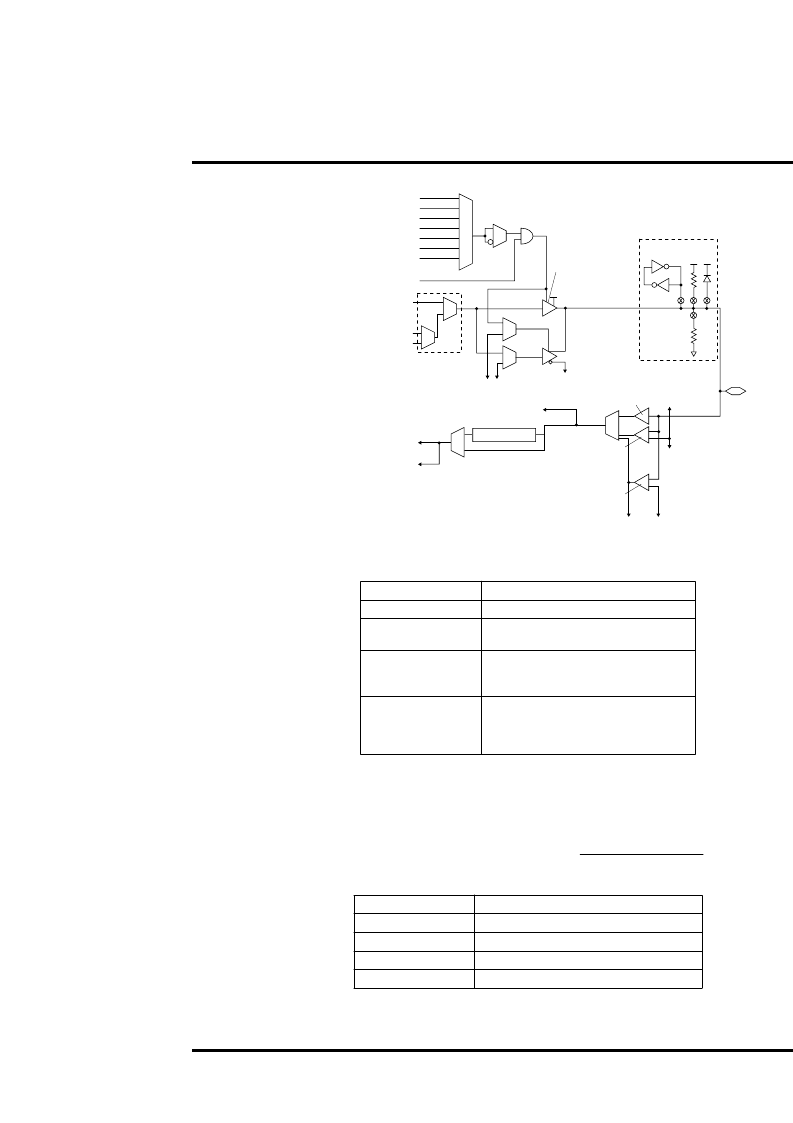

Figure 17. I/O Cell

Table 10. Shared PTOE Segments

sysIO Standards

Each I/O within a bank is individually con

fi

gurable based on the V

CCO

and V

REF

settings. Some standards also

require the use of an external termination voltage. Table 12 lists the sysIO standards with the typical values for

V

CCO,

V

REF

and V

TT.

For more information on the sysIO capability, please refer to Lattice technical note number

TN1000,

sysIO Usage Guidelines for Lattice Devices,

available at www.latticesemi.com.

Table 11. Number of I/Os per Bank

Device

MFBs Associated With Segments

(A, B, C, D) (E, F, G, H)

(A, B, C, D) (E, F, G, H)

(I, J, K, L) (M, N, O, P)

(A, B, C, D) (E, F, G, H)

(I, J, K, L) (M, N, O, P)

(Q, R, S, T) (U, V, W, Z)

(A, B, C, D) (E, F, G, H)

(I, J, K, L) (M, N, O, P)

(Q, R, S, T) (U, V, W, Z)

(Y, Z, AA, AB) (AC, AD, AE, AF)

ispXPLD 5256MX

ispXPLD 5512MX

ispXPLD 5768MX

ispXPLD 51024MX

Device

Maximum Number of I/Os per Bank (n)

36

68

96

96

ispXPLD 5256MX

ispXPLD 5512MX

ispXPLD 5768MX

ispXPLD 51024MX

Shared PTOE 0

Shared PTOE 1

Shared PTOE 2

Shared PTOE 3

PTOE

GOE0

GOE1

TOE

V

to All

Other I/Os

in Bank

V

for

this Bank

Differential

I/O Buffer

To Primary

Macrocell

To Alternate

Macrocell

Delay Element

To Adjacent

I/O Pad

V

Dependent

Input Buff

V

to All

other I/Os in Bank

er

CMOS/TTL

Input Buffer

(V

REF

Independent)

I/O

Pad

GND

Data Output from

Primary Macrocell

Data Output from

Alternate Macrocells

Output Sharing

Array (OSA)

Data Input to Routing

To Adjacent I/O Pad

Differential

Output Buffer

Output Buffer

(V

CCO

Independent

for Open Drain

Outputs)

+

–

+

–

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LC5768MC-5F256C | 3.3V, 2.5V and 1.8V In-System Programmable eXpanded Programmable Logic Device XPLD⑩ Family |

| LC5768MC-5F484C | 3.3V, 2.5V and 1.8V In-System Programmable eXpanded Programmable Logic Device XPLD⑩ Family |

| LC5768MC-75F256C | 3.3V, 2.5V and 1.8V In-System Programmable eXpanded Programmable Logic Device XPLD⑩ Family |

| LC5768MC-75F484C | 3.3V, 2.5V and 1.8V In-System Programmable eXpanded Programmable Logic Device XPLD⑩ Family |

| LC801 | SILICON GATE ENHANCEMENT MODE RF POWER LDMOS TRANSISTOR |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LC5512MC-75Q208I | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 PROGRAM EXPANDED LOG RoHS:否 制造商:Lattice 系列: 存儲類型:EEPROM 大電池數(shù)量:128 最大工作頻率:333 MHz 延遲時間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| LC5512MC-75Q256C | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:3.3V, 2.5V and 1.8V In-System Programmable eXpanded Programmable Logic Device XPLD⑩ Family |

| LC5512MC-75Q256I | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:3.3V, 2.5V and 1.8V In-System Programmable eXpanded Programmable Logic Device XPLD⑩ Family |

| LC5512MC-75Q484C | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:3.3V, 2.5V and 1.8V In-System Programmable eXpanded Programmable Logic Device XPLD⑩ Family |

| LC5512MC-75Q484I | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:3.3V, 2.5V and 1.8V In-System Programmable eXpanded Programmable Logic Device XPLD⑩ Family |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。