- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄30730 > LC7152KM PLL FREQUENCY SYNTHESIZER, 80 MHz, PDSO24 PDF資料下載

參數(shù)資料

| 型號: | LC7152KM |

| 元件分類: | PLL合成/DDS/VCOs |

| 英文描述: | PLL FREQUENCY SYNTHESIZER, 80 MHz, PDSO24 |

| 封裝: | MFP-24 |

| 文件頁數(shù): | 7/11頁 |

| 文件大小: | 287K |

| 代理商: | LC7152KM |

Pin Description

Symbol

Pin No.

Function

Description of function

PIA

14

Side-A local oscillator signal

input

.

Side-A programmable divider. The input frequency ranges are as follows.

FA: Serial data

.

Bits DA0 to DA15 determine the divider ratios

Divider ratio N = 272 to 65535

PIB

16

Side-B local-oscillator signal

input

.

Side-B programmable divider

The input frequency ranges are the same as for PIA.

FB(→ FA): Determined by the serial data

.

Bits DB0 to DB15 determine the divider ratios

Divider ratio N= 272 to 65535

.

Serial data: Bit SB is the standby mode control bit

When SB = 1, standby mode is selected. In standby mode, side-B is

stopped, PIB is pulled down to VSS.

When SB = 0, normal operation is selected.

XIN

XOUT

1

24

Crystal oscillator

.

Crystal oscillator connections (CI

% 50 Ω,CL % 16pF).

Note) When using a crystal other than as indicated above, its compatibility

with the crystal oscillator must be thoroughly studied.

PDA1

PDB1

10

22

Side-A main charge pump

Side-B main charge pump

.

These are PLL charge pump outputs that output the PLL phase error

signals. When the frequency generated by dividing the local oscillator signal

frequency by N is higher than the reference frequency, the charge pump

outputs a high-level signal for the phase error; when lower, the charge pump

outputs a low-level signal for the phase error.

If the two values match, these pins go to high-impedance.

.

fosc/N > fref or leading

→ Positive Pulse

.

fosc/N < fref or lagging

→ Negative Pulse

.

fosc/N = fref and coincidence

→ High-Impedance

(*SB = [1] : PDB1 → High-Impedance)

PDA2

PDB2

9

23

Side-A sub charge pump

Side-B sub charge pump

.

PLL charge pump output; outputs PLL phase error signal only when the

unlock condition is detected.

.

The unlock detection threshold is set by serial data bits UL0 and UL1.

.

When a phase error that is shorter than the detection threshold occurs, this

signal goes to high impedance and the phase error signal for the main

charge pump is output.

.

The output pulse of the phase error signal has the same polarity as the main

charge pump.

LDA

LDB

6

5

Side-A unlock detector output

Side-B unlock detector output

.

Outputs the PLL lock/unlock status.

Locked: Open

Unlocked: Low

.

The unlock detection threshold for lock/unlock discrimination is set by serial

data bits UL0 and UL1.

.

The output phase error extension is set by serial data bits UE0 and UE1.

.

For details, refer to the description of the serial data.

.

SB=1:LDB → Open

AIA

AOA

AIB

OAB

11

12

21

20

Side-A low-pass filter transistor

Side-B low-pass filter transistor

.

MOS N-channel transistor for the PLL filter

.

The AOA and AOB output withstand voltage is 13V.

OUTA

OUTB

13

19

Side-A general purpose

output port

Side-B general purpose

output port

.

These latch the serial data bits OA and OB that are sent from the controller,

and then invert and output the data.

(OUTA can also output XIN divided by two.

.

In the LC7152NM, OUTA and OUTB are open at the power-on reset.

FA = [0]

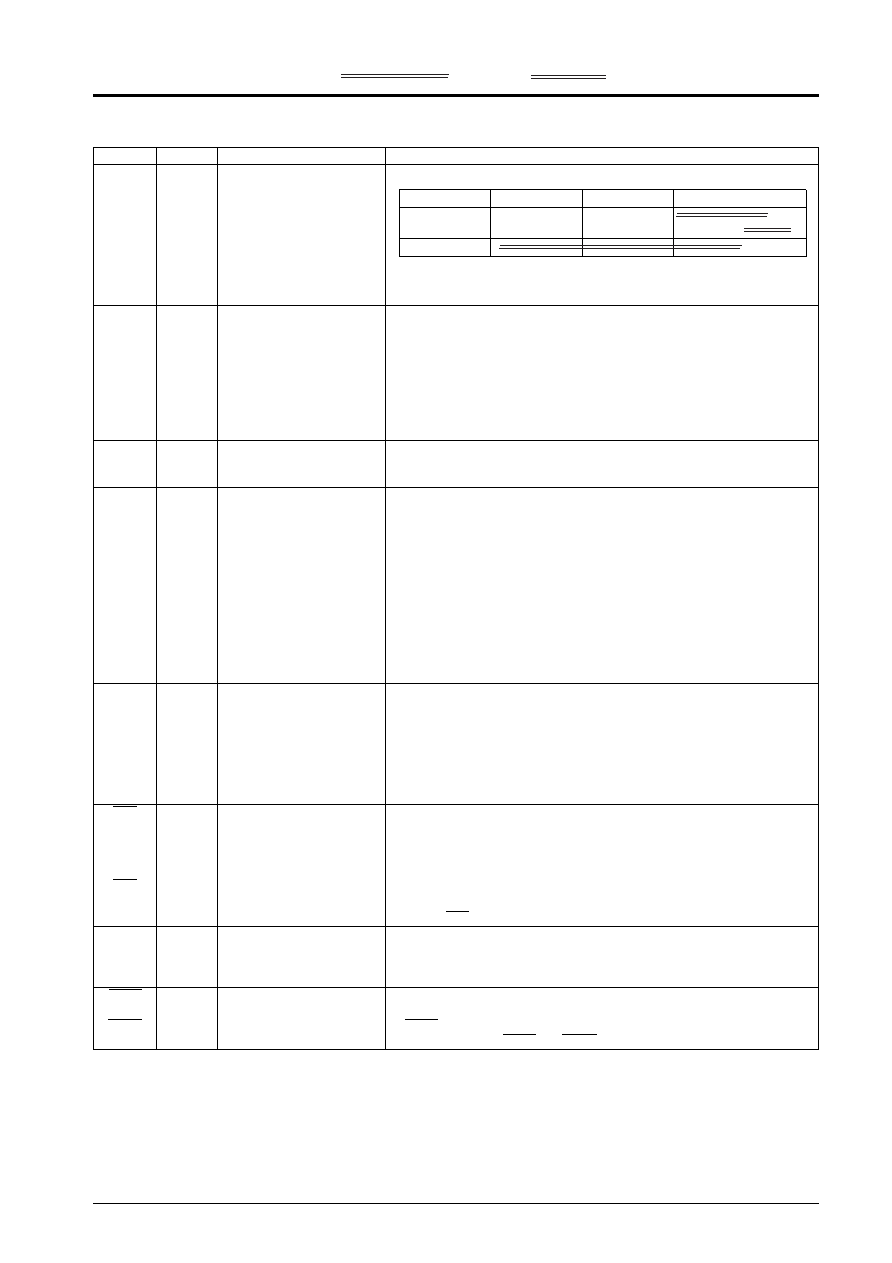

FA = [1]

VDD

Device

1.5 to 23 MHz

20 to 55 MHz

2.0 to 3.3 V

LC7152, 7152M

LC7152NM, 7152KM

—————

55 to 80 MHz

2.7 to 3.3 V

LC7152KM

For more information on crystal oscillator : Nihon Dempa Kogyo Co., Ltd.

Continued on next page.

LC7152, 7152M, 7152NM, 7152KM

No.3889-5/13

相關PDF資料 |

PDF描述 |

|---|---|

| LC7152NM | PLL FREQUENCY SYNTHESIZER, 55 MHz, PDSO24 |

| LC7152 | PLL FREQUENCY SYNTHESIZER, 55 MHz, PDIP24 |

| LC72131KM | PLL FREQUENCY SYNTHESIZER, 40 MHz, PDSO20 |

| LC72133V | PLL FREQUENCY SYNTHESIZER, 40 MHz, PDSO20 |

| LC72133M | PLL FREQUENCY SYNTHESIZER, 40 MHz, PDSO20 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| LC7152M | 制造商:SANYO 制造商全稱:Sanyo Semicon Device 功能描述:Universal Dual-PLL Frequency Synthesizers |

| LC7152NM | 制造商:SANYO 制造商全稱:Sanyo Semicon Device 功能描述:Universal Dual-PLL Frequency Synthesizers |

| LC7152NMA-AH | 功能描述:時鐘合成器/抖動清除器 RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

| LC7153 | 制造商:SANYO 制造商全稱:Sanyo Semicon Device 功能描述:Universal Dual-PLL Frequency Synthesizers |

| LC7153M | 制造商:SANYO 制造商全稱:Sanyo Semicon Device 功能描述:Universal Dual-PLL Frequency Synthesizers |

發(fā)布緊急采購,3分鐘左右您將得到回復。