- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄30731 > LC72711W SPECIALTY CONSUMER CIRCUIT, PQFP64 PDF資料下載

參數(shù)資料

| 型號(hào): | LC72711W |

| 元件分類: | 消費(fèi)家電 |

| 英文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP64 |

| 封裝: | 10 X 10 MM, SQFP-64 |

| 文件頁(yè)數(shù): | 20/26頁(yè) |

| 文件大?。?/td> | 157K |

| 代理商: | LC72711W |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)當(dāng)前第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)

LC72711W, 72711LW

No.6167-3/26

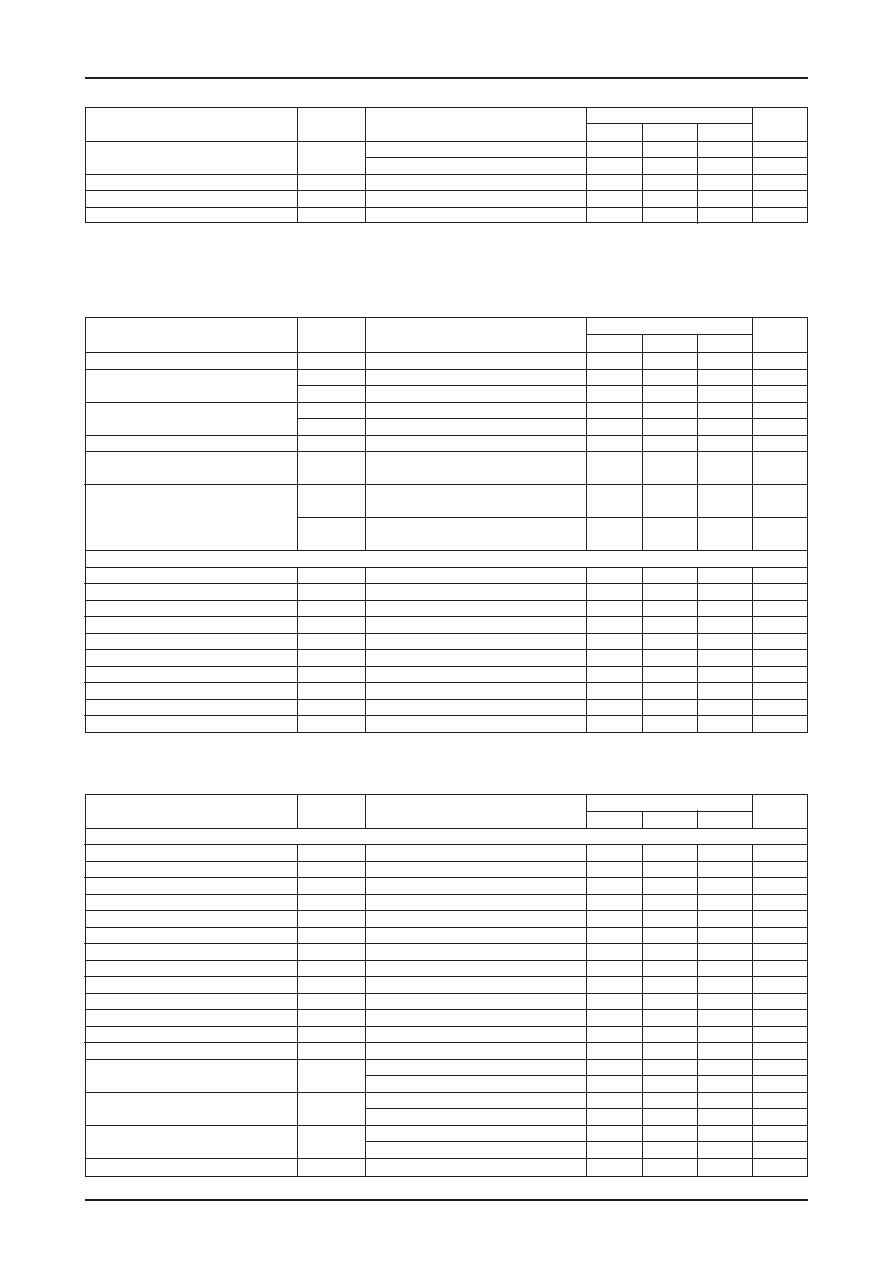

Continued from preceding page.

Ratings

Parameter

Symbol

Conditions

min

typ

max

Unit

RDY width (corrected output read)

tWDRDY

RDY (BUSWD=L 8bits)

60

210

nS

RDY ((BUSWD=H 16bits)

300

490

nS

DACK to DREQ delay

tDREQ

DREQ, DACK

260

nS

DMA cycle wait

tCYDM

RD, DREQ

420

nS

RD low-level width (DMA)

tWRDM

RD

300

nS

Notes: Application designs must take the RDY signal output delay into consideration if the RDY signal is used as the CPU bus wait signal.

If the RDY signal is not used, (that is, if no wait states are inserted) the value of the RD low-level width will be 250ns (minimum).

[LC72711LW]

Allowable Operating Ranges at Ta=-40 to +85°C, VSS=0V

Ratings

Parameter

Symbol

Conditions

min

typ

max

Unit

Supply voltage

VDD

2.7

3.6

V

High-level input voltage

VIH1

A0/CL, A1/CE, A2/DI, RST, STNBY

0.7VDD

5.5

V

VIH2

DACK, WR, RD, CS, SP, BUSWD, A3, IOCNT1, IOCNT2

0.7VDD

VDD

V

Low-level input voltage

VIL1

Pins for which VIH1 applies

VSS

0.3VDD

V

VIL2

Pins for which VIH2 applies

VSS

0.3VDD

V

Oscillator frequency

FOSC

This IC operates with a frequency precision of ±250 ppm

7.2

MHz

XIN input sensitivity

VXI

With a sine wave input to XIN, capacitor coupling,

400

900

mVrms

VDD=+2.7 to +3.6V

VMPX1

With a 100% modulated composite signal input to

120

350

mVrms

Input amplitude

MPXIN, VDD=+3.3V

VMPX2

With a 100% modulated composite signal input to

120

180

mVrms

MPXIN, VDD=+2.7V

[Serial I/O]

Clock low-level period

tCL

A0/CL

0.7

S

Clock high-level period

tCH

A0/CL

0.7

S

Data setup time

tSU

A0/CL, A2/DI

0.7

S

Data hold time

tHD

A0/CL, A2/DI

0.7

S

CE wait time

tEL

A0/CL, A1/CE

0.7

S

CE setup time

tES

A0/CL, A1/CE

0.7

S

CE hold time

tEH

A0/CL, A1/CE

0.7

S

Data latch change time

tLC

A1/CE

0.7

S

Data output time

tDDO

DO, A0/CL

277

555

nS

CRC4 change time

tCRC

CRC4, A0/CL

0.7

S

[LC72711LW]

Allowable Operating Ranges: Parallel Interface at Ta=-40 to +85°C, VSS=0V

Ratings

Parameter

Symbol

Conditions

min

typ

max

Unit

[Parallel I/O]

Address to RD setup

tSARD

A0/CL, A1/CE, A2/DI, A3, RD

20

nS

RD to address hold

tHARD

A0/CL, A1/CE, A2/DI, A3, RD, tWRDL=>250ns

-20

nS

RD low-level width

tWRDL1

RD

280

nS

RD low-level width (when RDY is used)

tWRDL2

RD

100

nS

RD cycle wait

tCYRD

A0/CL, A1/CE, A2/DI, A3, RD

150

nS

RDY width (Register read)

tWRDY

RDY

60

230

nS

RD data hold

tRDH

RD, DATn

0

nS

Address to WR setup

tSAWR

A0/CL, A1/CE, A2/DI, A3, WR

20

nS

WR to address hold

tHAWR

A0/CL, A1/CE, A2/DI, A3, WR

20

nS

WR cycle wait

tCYWR

A0/CL, A1/CE, A2/DI, A3, WR

150

nS

WR low-level width

tWWRL

WR

200

nS

WR data hold

tWDH

WR, DATn

0

nS

RDY output delay

tDRDY

RD, RDY

0

50

nS

Corrected output RD width

tWDRD1

RD (BUSWD=L 8bits)

300

nS

RD (BUSWD=H 16bits)

540

nS

Corrected output RD width

tWDRD2

RD (BUSWD=L 8bits)

100

nS

(when RDY is used)

RD (BUSWD=H 16bits)

300

nS

RDY width (corrected output read)

tWDRDY

RDY (BUSWD=L 8bits)

60

230

nS

RDY ((BUSWD=H 16bits)

300

490

nS

DACK to DREQ delay

tDREQ

DREQ, DACK

260

nS

Continued on next page.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LC72711LW | SPECIALTY CONSUMER CIRCUIT, PQFP64 |

| LC72713W | SPECIALTY CONSUMER CIRCUIT, PQFP64 |

| LC72713W | SPECIALTY CONSUMER CIRCUIT, PQFP64 |

| LC72714W | SPECIALTY CONSUMER CIRCUIT, PQFP64 |

| LC72714W | SPECIALTY CONSUMER CIRCUIT, PQFP64 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LC72711W_12 | 制造商:SANYO 制造商全稱:Sanyo Semicon Device 功能描述:Mobile FM Multiplex Broadcast (DARC) Receiver IC |

| LC72713W | 制造商:未知廠家 制造商全稱:未知廠家 功能描述: |

| LC72714 | 制造商:SANYO 制造商全稱:Sanyo Semicon Device 功能描述:Mobile FM Multiplex Broadcast IC with On-Chip VICS Decoder |

| LC72714W | 制造商:SANYO 制造商全稱:Sanyo Semicon Device 功能描述:Mobile FM Multiplex Broadcast IC with On-Chip VICS Decoder |

| LC72715PW | 制造商:SANYO 制造商全稱:Sanyo Semicon Device 功能描述:CMOS IC Mobile FM Multiplex Broadcast IC with On-Chip VICS Decoder |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。