- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄30731 > LC72720 SPECIALTY CONSUMER CIRCUIT, PDIP24 PDF資料下載

參數(shù)資料

| 型號(hào): | LC72720 |

| 元件分類(lèi): | 消費(fèi)家電 |

| 英文描述: | SPECIALTY CONSUMER CIRCUIT, PDIP24 |

| 封裝: | SDIP-24 |

| 文件頁(yè)數(shù): | 1/14頁(yè) |

| 文件大小: | 234K |

| 代理商: | LC72720 |

當(dāng)前第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)

CMOS LSI

Ordering number : EN *5602

N2897HA (OT) No. 5602-1/14

Preliminary

LC72720, 72720M

SANYO Electric Co.,Ltd. Semiconductor Bussiness Headquarters

TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110 JAPAN

Overview

The LC72720 and LC72720M are single-chip system LSIs

that implement the signal processing required by the

European Broadcasting Union RDS (Radio Data System)

standard and by the US NRSC (National Radio System

Committee) RDBS (Radio Broadcast Data System)

standard. These LSIs include band-pass filter,

demodulator, synchronization, and error correction circuits

as well as data buffer RAM on chip and perform effective

error correction using a soft-decision error correction

technique.

Functions

Band-pass filter: Switched capacitor filter (SCF)

Demodulator: RDS data clock regeneration and

demodulated data reliability information

Synchronization: Block synchronization detection (with

variable backward and forward protection conditions)

Error correction: Soft-decision/hard-decision error

correction

Buffer RAM: Adequate for 24 blocks of data (about 500

ms) and flag memory

Data I/O: CCB interface (power on reset)

Features

Error correction capability improved by soft-decision

error correction

The load on the control microprocessor can be reduced

by storing decoded data in the on-chip data buffer RAM.

Two synchronization detection circuits provide

continuous and stable detection of the synchronization

timing.

Data can be read out starting with the backward-

protection block data after a synchronization reset.

Fully adjustment free

Operating power-supply voltage: 4.5 to 5.5 V

Operating temperature: –40 to +85°C

Package: DIP24S, MFP24

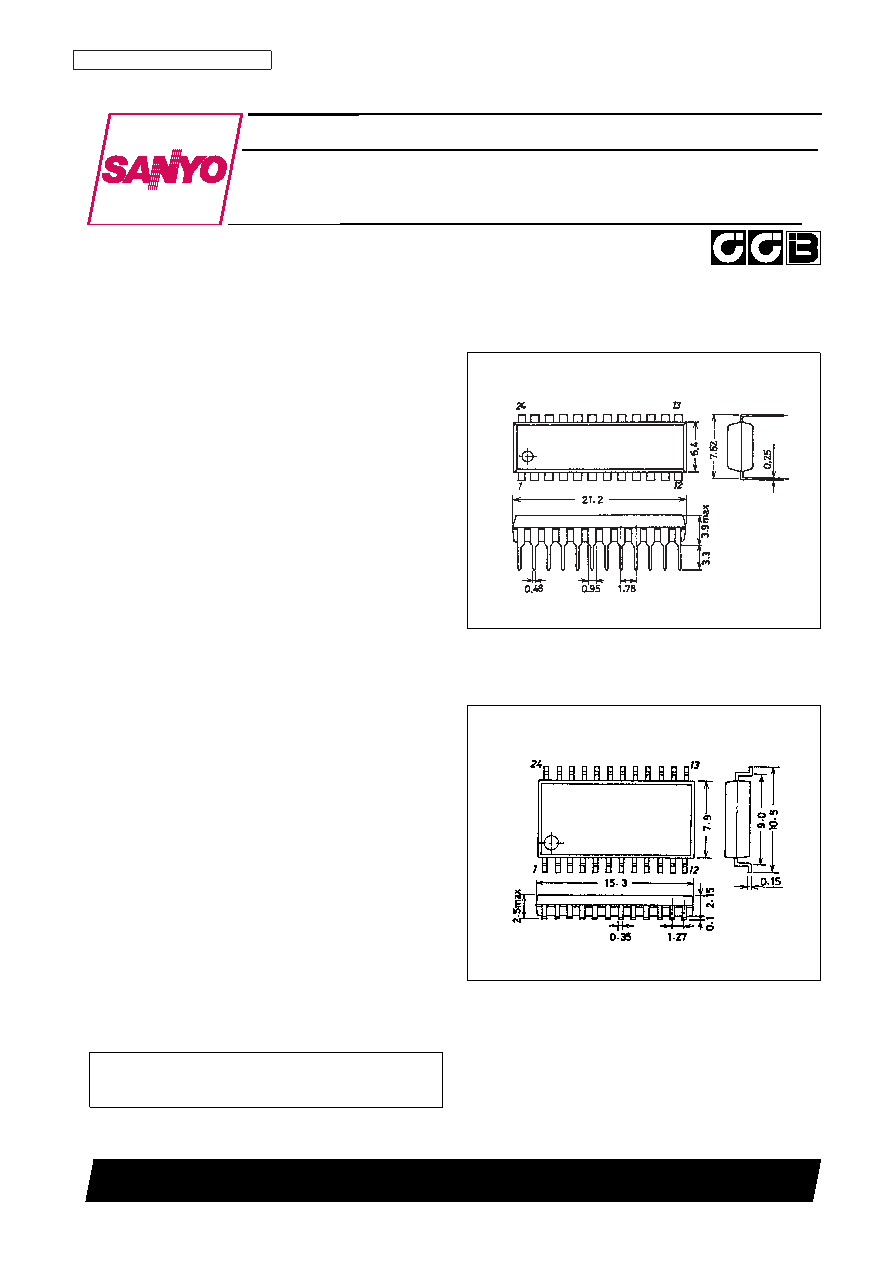

Package Dimensions

unit: mm

3067-DIP24S

unit: mm

3045B-MFP24

SANYO: DIP24S

[LC72720]

SANYO: MFP24

[LC72720M]

CCB is a trademark of SANYO ELECTRIC CO., LTD.

CCB is SANYO’s original bus format and all the bus

addresses are controlled by SANYO.

Single-Chip RDS

Signal-Processing System LSI

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LC72720M | SPECIALTY CONSUMER CIRCUIT, PDSO24 |

| LC72722M | SPECIALTY CONSUMER CIRCUIT, PDSO24 |

| LC72722 | SPECIALTY CONSUMER CIRCUIT, PDIP24 |

| LC72722M | SPECIALTY CONSUMER CIRCUIT, PDSO24 |

| LC72722PM | SPECIALTY CONSUMER CIRCUIT, PDSO24 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LC72720M | 制造商:SANYO 制造商全稱(chēng):Sanyo Semicon Device 功能描述:Single-Chip RDS Signal-Processing System LSI |

| LC72720N | 制造商:SANYO 制造商全稱(chēng):Sanyo Semicon Device 功能描述:Single-Chip RDS Signal-Processing System LSI |

| LC72720NM | 制造商:SANYO 制造商全稱(chēng):Sanyo Semicon Device 功能描述:Single-Chip RDS Signal-Processing System LSI |

| LC72720Y | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述: |

| LC72720YV | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。