- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄30731 > LC72722M (SANYO SEMICONDUCTOR CO LTD) SPECIALTY CONSUMER CIRCUIT, PDSO24 PDF資料下載

參數(shù)資料

| 型號: | LC72722M |

| 廠商: | SANYO SEMICONDUCTOR CO LTD |

| 元件分類: | 消費(fèi)家電 |

| 英文描述: | SPECIALTY CONSUMER CIRCUIT, PDSO24 |

| 封裝: | MFP-24 |

| 文件頁數(shù): | 13/15頁 |

| 文件大?。?/td> | 114K |

| 代理商: | LC72722M |

No. 5602-7/15

LC72722, 72722M, 72722PM

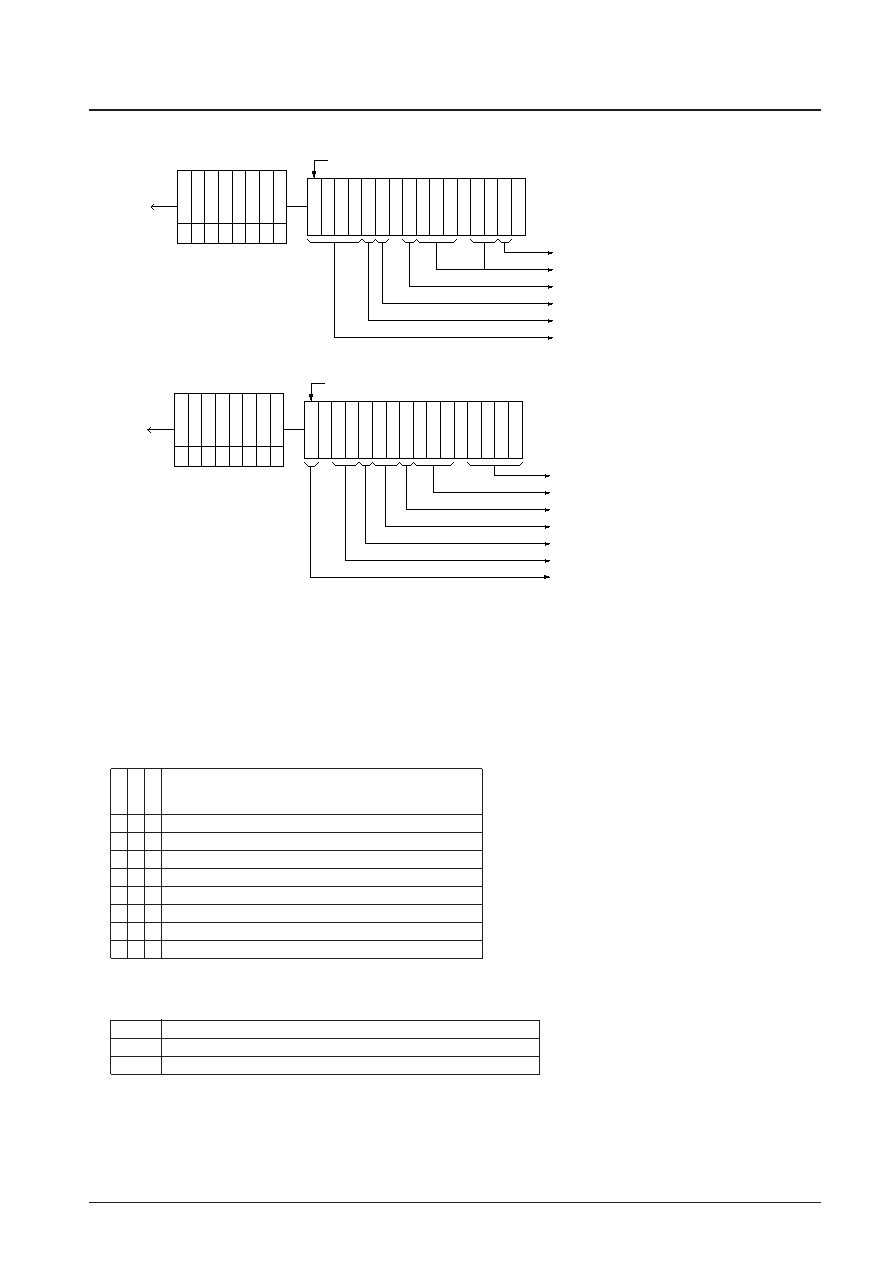

CCB Input Data Format

Caution: The bits labeled with an asterisk must be set to 0.

1. Synchronization protection (forward protection) method setting (4 bits): FS0 to FS3

FS3 = 0: If offset words in the correct order could not be detected continuously during the number of blocks specified

by FS0 to FS2, take that to be a lost synchronization state.

FS3 = 1: If blocks with uncorrectable errors were received consecutively during the number of blocks specified by

FS0 to FS2, take that to be a lost synchronization state.

Initial value: FS0 = 0, FS1 = 1, FS2 = 0, FS3 = 0

Initial value: BS = 0

F

S

Condition for detecting lost synchronization

0

1

2

0

If 3 consecutive blocks matching the FS3 condition are received.

1

0

If 4 consecutive blocks matching the FS3 condition are received.

0

1

0

If 5 consecutive blocks matching the FS3 condition are received.

1

0

If 6 consecutive blocks matching the FS3 condition are received.

0

1

If 8 consecutive blocks matching the FS3 condition are received.

1

0

1

If 10 consecutive blocks matching the FS3 condition are received.

0

1

If 12 consecutive blocks matching the FS3 condition are received.

1

If 16 consecutive blocks matching the FS3 condition are received.

2. Synchronization detection method setting (1 bit): BS

BS

Synchronization detection conditions

0

If, during 3 blocks, 2 blocks of offset words were detected in the correct order.

1

If the offset words were detected in the correct order in 2 consecutive blocks.

DI

B

0

0 1 0 1

0 1 1 0

B

1

B

2

B

3

A

0

A

1

A

2

A

3

F

S

0

F

S

1

F

S

2

F

S

3

E

C

0

E

C

3

E

C

4

C

T

0

E

C

1

E

C

2

B

S

Y

R

*

O

W

E

[1] CCB address 6A

[2] CCB address 6B

IN1 data, first bit

IN2 data, first bit

(12) Circuit control

(5) Error correction method setting

(4) RAM write control

(3) Synchronization and RAM address reset

(2) Synchronization detection method setting

(1) Synchronization protection method setting

(11) Test mode settings

(10) Output pin settings

(9) RDS/RBDS selection

(8) Demodulation circuit phase control

(7) Crystal oscillator frequency selection

(6) Intermittent DO output setting

(12) Circuit control

DI

B

0

1 1 0 1

0 1 1 0

B

1

B

2

B

3

A

0

A

1

A

2

A

3

C

T

1

S

P

0

S

P

1

P

T

0

T

S

0

T

S

1

T

S

2

T

S

3

P

T

1

P

T

2

X

S

P

L

0

P

L

1

*

R

M

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LC72722PM | SPECIALTY CONSUMER CIRCUIT, PDSO24 |

| LC72722 | SPECIALTY CONSUMER CIRCUIT, PDIP24 |

| LC72722PM | SPECIALTY CONSUMER CIRCUIT, PDSO24 |

| LC72723M | SPECIALTY CONSUMER CIRCUIT, PDSO16 |

| LC72723 | SPECIALTY CONSUMER CIRCUIT, PDIP16 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LC72722PM | 制造商:SANYO 制造商全稱:Sanyo Semicon Device 功能描述:Single-Chip RDS Signal-Processing System LSI |

| LC72722PM_12 | 制造商:SANYO 制造商全稱:Sanyo Semicon Device 功能描述:Single-Chip RDS Signal-Processing System IC |

| LC72722PM-MPB-E | 功能描述:音頻 DSP RoHS:否 制造商:Texas Instruments 工作電源電壓: 電源電流: 工作溫度范圍: 安裝風(fēng)格: 封裝 / 箱體: 封裝:Tube |

| LC72722PMS | 制造商:SANYO 制造商全稱:Sanyo Semicon Device 功能描述:Single-Chip RDS Signal-Processing System IC |

| LC72722PMS-MPB-E | 制造商:ON Semiconductor 功能描述:RDS/RBDS DECODE-IC - Ammo Pack |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。