- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄30734 > LC74793JM SPECIALTY CONSUMER CIRCUIT, PDSO24 PDF資料下載

參數(shù)資料

| 型號: | LC74793JM |

| 元件分類: | 消費家電 |

| 英文描述: | SPECIALTY CONSUMER CIRCUIT, PDSO24 |

| 封裝: | MFP-24 |

| 文件頁數(shù): | 2/24頁 |

| 文件大小: | 154K |

| 代理商: | LC74793JM |

No. 5966-10/24

LC74793, 74793JM

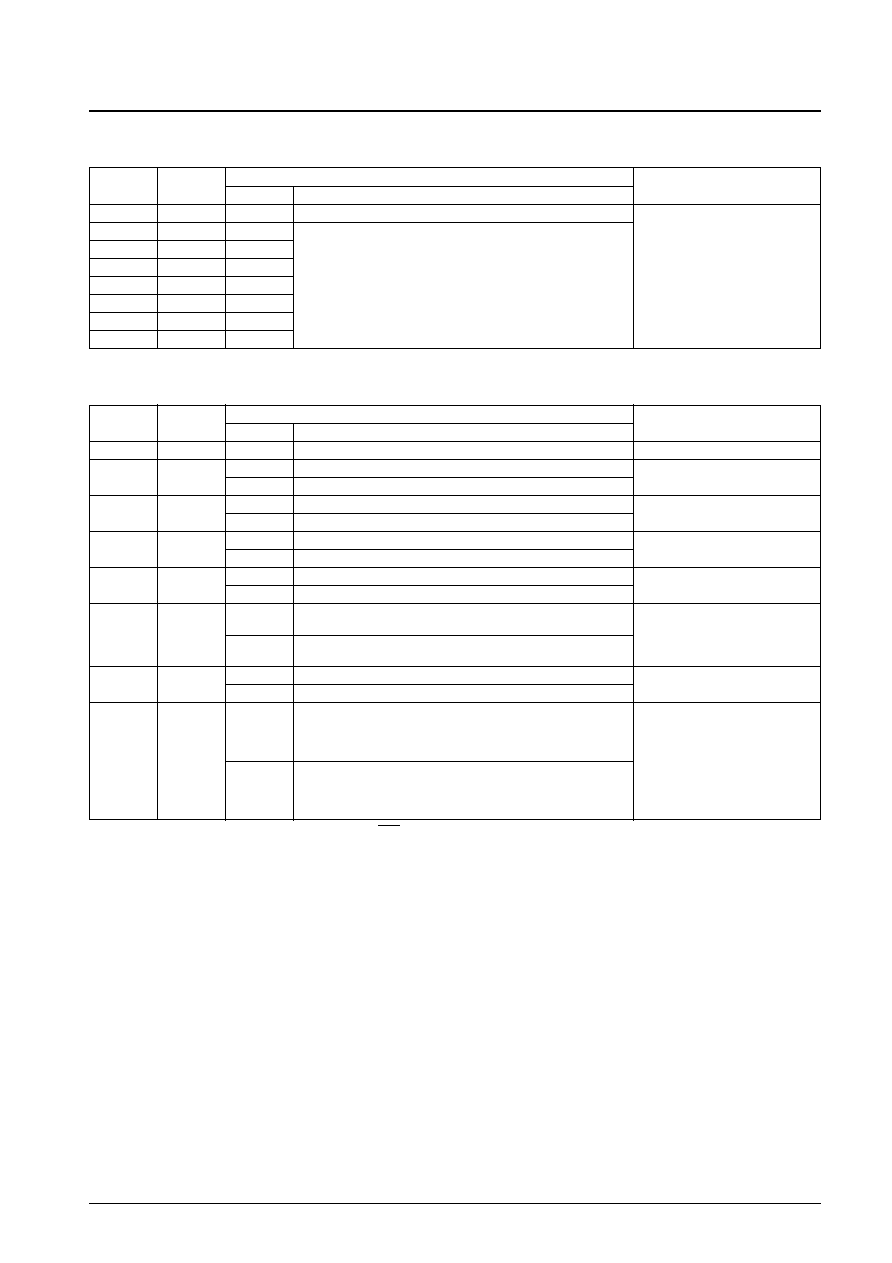

Command 2 (VPS/PDC control command 2)

First byte

DA 0 to 7

Register

Contents

Notes

Status

Function

7

—

1

First byte identification bit

6

—

1

Command 2 identification code.

5

—

1

VPS/PDC control settings 2.

4

—

1

3

—

0

2

—

0

1

—

1

0

—

0

Second byte

DA 0 to 7

Register

Contents

Notes

Status

Function

7

—

0

Second byte identification bit

6

VMWSE2

0

From the vertical mask period start return period

CPOUT pin vertical mask period

1

From 10H before the vertical mask period start return period

switching 2

5

VMWSEL

0

The vertical mask period is the return period

CPOUT pin vertical mask period

1

The vertical mask period is 9H

switching

4

HBS2

0

Clock run discrimination 1 (2 times)

Clock run discrimination circuit setting

1

Clock run discrimination 2 (4 times)

3

HBS1

0

Framing code discrimination 1

Framing code discrimination selection

1

Framing code discrimination 2 (A single bad bit is ignored)

0

Error check enabled (The error check can be turned on or off on

2

BMS

per-byte basis.)

1

Error check disabled (Applications can select whether data with errors

is held or written for each byte.)

1

EMS

0

Data hold

1

Data write (Error bits are set to 0 in VPS mode)

Error check turned on for unused bytes

0

VPS: bytes 3, 4, and 6 to 10, PDC: bytes 7 to 12

Header 1: bytes 14 to 37, 2: 14 to 29, 3 14 to 21.

0

DCE

Status 1 (3): bytes 7 to 25, status 2 (4) bytes 7 to 35.

Error check turned off for unused bytes

1

VPS: bytes 3, 4, and 6 to 10, PDC: bytes 7 to 12

Header 1: bytes 14 to 37, 2: 14 to 29, 3 14 to 21.

Status 1 (3): bytes 7 to 25, status 2 (4) bytes 7 to 35.

When set to 0: If there are no errors in bytes

for which the error check is turned on, those

bytes will be written to P-S (COM7-9).

When set to 1: Data is written to P-S

regardless of whether or not errors occurred.

When error checking is enabled, specifies the

processing when an error occurs in a byte for

which error checking was turned off

Error check setting for unused data

bytes

Biphase (VPS),

Hamming (PDC),

Odd parity (header)

Note: All registers are cleared to 0 when the IC is reset by the RST pin.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LC74793 | SPECIALTY CONSUMER CIRCUIT, PDIP24 |

| LC74793JM | SPECIALTY CONSUMER CIRCUIT, PDSO24 |

| LC74793 | SPECIALTY CONSUMER CIRCUIT, PDIP24 |

| LC74794M | ON-SCREEN DISPLAY IC, PDSO30 |

| LC74794 | ON-SCREEN DISPLAY IC, PDIP30 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LC74793JM-TLM-E | 制造商:ON Semiconductor 功能描述:Data Converter ICs - Various VPS/PDC SLICER IC 制造商:ON Semiconductor 功能描述:REEL / VPS/PDC SLICER IC |

| LC74794 | 制造商:SANYO 制造商全稱:Sanyo Semicon Device 功能描述:On-Screen Display Controller LSI |

| LC74794M | 制造商:SANYO 制造商全稱:Sanyo Semicon Device 功能描述:On-Screen Display Controller LSI |

| LC74795 | 制造商:SANYO 制造商全稱:Sanyo Semicon Device 功能描述:On-Screen Display Controller LSI |

| LC74795M | 制造商:SANYO 制造商全稱:Sanyo Semicon Device 功能描述:On-Screen Display Controller LSI |

發(fā)布緊急采購,3分鐘左右您將得到回復。