- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄30736 > LC82161B-E SPECIALTY CONSUMER CIRCUIT, PQFP208 PDF資料下載

參數(shù)資料

| 型號: | LC82161B-E |

| 元件分類: | 消費家電 |

| 英文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP208 |

| 封裝: | SQFP-208 |

| 文件頁數(shù): | 8/19頁 |

| 文件大?。?/td> | 225K |

| 代理商: | LC82161B-E |

LC82161B-E

No.7775-16/19

Interrupt Controller

This interrupt controller circuit supports 23 internal interrupts and 3 external interrupts.

Two interrupt vectors (FIQ/IRQ)

The interrupt is recognized using the status register. Interrupt priority is controlled in software.

Either rising edge detection, falling edge detection, or level detection can be selected for the external interrupts.

Interrupts can be enabled/disabled on a per-interrupt basis.

The FIQ or IRQ vector can be selected for each interrupt.

Noise filters are available to remove noise from interrupts 1 and 2.

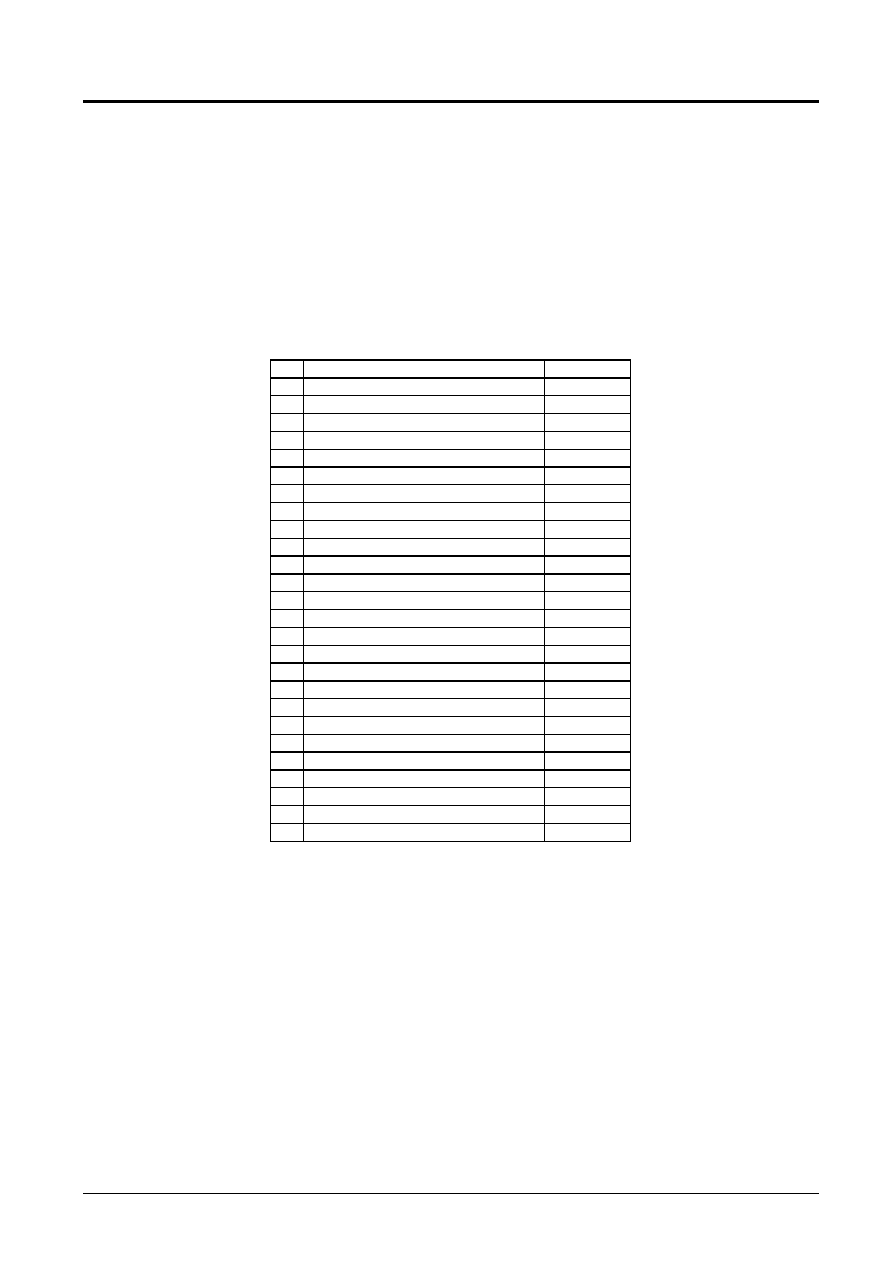

Table 2 Interrupt Allocation

No.

Interrupt

Internal/external

1

External interrupt 1

External

External interrupt 2

External

3

External interrupt 3

External

4

DSP1

Internal

5

DSP2

Internal

6

DSP3

Internal

7

DSP4

Internal

8

DSP5

Internal

9

DSP6

Internal

10

DSP7

Internal

11

DSP8

Internal

12

Watchdog timer

Internal

13

Basic timer

Internal

14

DMA controller, channel 1

Internal

15

DMA controller, channel 2

Internal

16

SIO

Internal

17

USART1

Internal

18

USART2

Internal

19

GPIO

Internal

20

Protocol engine

Internal

21

Multifunction timer, channel 1: compare match A

Internal

22

Multifunction timer, channel 1: compare match B

Internal

23

Multifunction timer, channel 1: overflow

Internal

24

Multifunction timer, channel 2: compare match A

Internal

25

Multifunction timer, channel 2: compare match B

Internal

26

Multifunction timer, channel 2: overflow

Internal

DMA Controller

The LC82161B provides a 2-channel DMA controller.

Channel 1 is allocated to the protocol engine transmission port, and channel 2 is allocated to the protocol engine reception

port.

Memory to memory transfers

The transfer start operation can be performed either in software or by a DREQ start.

Transfer units: byte, half word, word

Provides single and block transfer modes

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LC8220 | SPECIALTY CONSUMER CIRCUIT, PQFP160 |

| LC82210 | SPECIALTY CONSUMER CIRCUIT, PQFP100 |

| LC82220 | SPECIALTY CONSUMER CIRCUIT, PQFP128 |

| LC8230 | SPECIALTY CONSUMER CIRCUIT, PQFP100 |

| LC823231 | SPECIALTY CONSUMER CIRCUIT, PQFP64 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LC821621-E | 制造商:ON Semiconductor 功能描述:VOIP PROCESSOR - Trays |

| LC82162BL-E | 制造商:ON Semiconductor 功能描述:VOIP PROCESSOR - Trays |

| LC82162B-R1000-E | 制造商:ON Semiconductor 功能描述:VOIP PROCESSOR - Trays 制造商:ON Semiconductor 功能描述:Processors - Application Specialized |

| LC8220 | 制造商:SANYO 制造商全稱:Sanyo Semicon Device 功能描述:JPEG Still Color Image Compression/Decompression LSI |

| LC82-2001G | 制造商:SEI Stackpole Electronics Inc 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。