- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄367549 > LG1600KXH2666 LG1600KXH Clock and Data Regenerator PDF資料下載

參數(shù)資料

| 型號: | LG1600KXH2666 |

| 英文描述: | LG1600KXH Clock and Data Regenerator |

| 中文描述: | LG1600KXH時鐘和數(shù)據(jù)再生 |

| 文件頁數(shù): | 2/20頁 |

| 文件大小: | 492K |

| 代理商: | LG1600KXH2666 |

Data Sheet

August 1999

LG1600FXH Clock and Data Regenerator

2

Lucent Technologies Inc.

Functional Description

The LG1600FXH Clock and Data Regenerator (CDR)

is a compact, single device solution to clock recovery

and data retiming in high-speed communication sys-

tems such as fiber-optic data links and long-span fiber-

optic regenerators and terminals. Using frequency and

phase-lock loop (FPLL) techniques, the device regen-

erates clean clock and error-free data signals from a

nonreturn-to-zero (NRZ) data input, corrupted by jitter

and intersymbol interference. The LG1600FXH

exceeds ITU-T/Bellcore jitter tolerance requirements

for SONET/SDH systems.

The device houses two integrated circuits on an alu-

mina substrate inside a hermetically sealed 3 cm

×

3 cm (1.2 in.

×

1.2 in.) surface-mount package: a GaAs

IC that contains the high-speed part of an FPLL as well

as a highly sensitive decision circuit; and a silicon bipo-

lar IC that contains a loop filter, acquisition, and signal

detect circuitry.

The two ac-coupled complementary data inputs can be

driven differentially as well as single ended. A dc feed-

back voltage V

–FB

maintains a data input threshold

V

–TH

(decision level) that is optimum for a wide range

of 50% duty cycle input levels (connect to V

–TH

). If

needed, the user can supply an external threshold to

compensate for different mark densities or distorted

input signals (see Figure 10).

Regenerated clock and data are available from comple-

mentary outputs that can either be ac coupled, to pro-

vide 50

output match, or dc coupled with 50

to

ground at the receiving end.

The second-order PLL filter bandwidth is set by the

user with an external resistor between pin 11 and

ground (required). An internal capacitor provides suffi-

cient PLL damping for most applications. In critical

applications, PLL damping can be increased using an

external capacitor between pins 9 and 11.

The device is powered by a single –5.2 V ECL compat-

ible supply and typically consumes 1.5 W.

The LG1600FXH comes in standard bit rates, but can

be factory tuned for any rate between 500 Mbits/s and

5500 Mbits/s.

A test fixture (TF1004A) with SMA connectors is avail-

able to allow quick evaluation of the LG1600FXH.

Theory of Operation

A digital regenerator has the task of retransmitting a bit

stream that is received from a remote source with the

same fidelity at which it was originally transmitted.

Two basic properties of the digital signal need to be

restored: the timing of the transitions between the bits

and the value of each bit.

12-3225(F)r.6

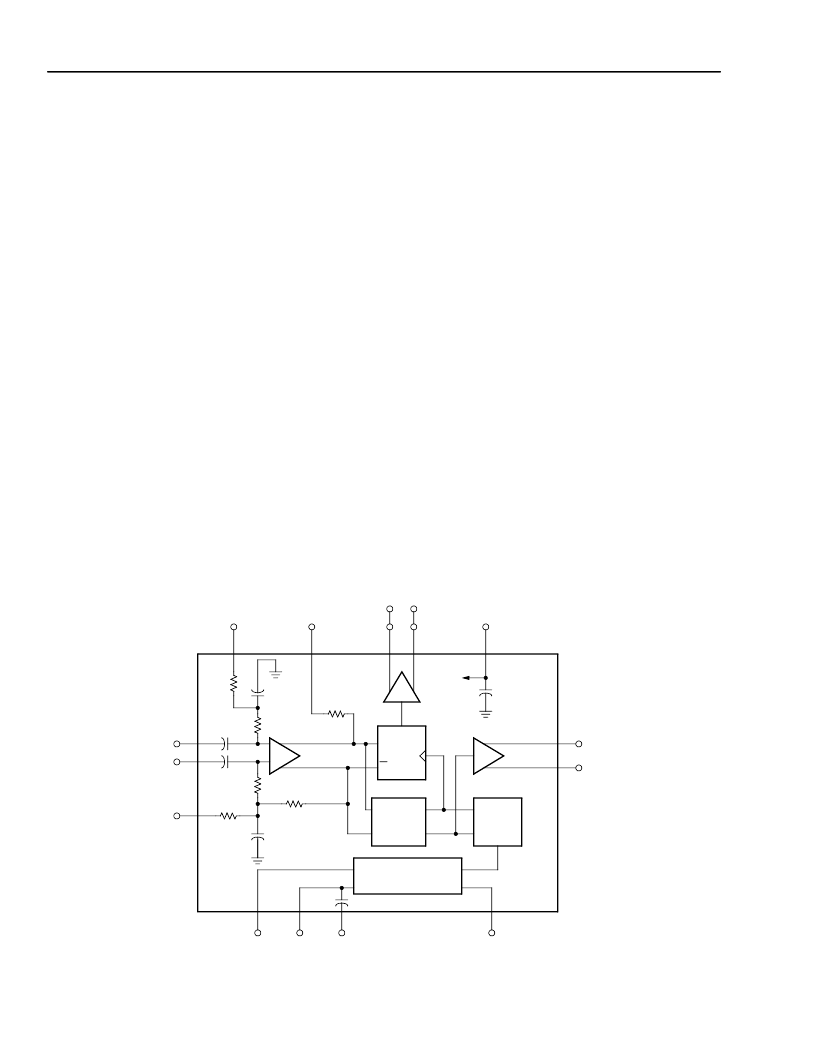

Figure 2. LG1600FXH Block Diagram

VCO

Q

D

V

+

CLKO

V

–

CLKO

31

26

D

FREQ. &

PHASE

DETECT.

90

°

LOOP CONTROL &

SIGNAL DETECT

11

9

7

V

REF

C

EXT

R

EXT

LOS

V

–TH

51

V

–FB

48

55

60

65

V

–IN

V

+IN

V

+FB

0.047

μ

F

0.047

μ

F

0.047

μ

F

0.047

μ

F

1 k

50

25 k

50

25 k

1 k

43

38

V

+

OUT

V

–

OUT

V

SS

35

0.047

μ

F

0.047

μ

F

0

°

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LG1600FXH5332 | LG1600FXH Clock and Data Regenerator |

| LG1600FXH | Clock and Data Regenerator(時鐘數(shù)據(jù)再生器) |

| LG1602 | LG1602 Decision Circuit |

| LG1602AXB | LG1602 Decision Circuit |

| LG1602BXB | LG1602 Decision Circuit |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LG1601281 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:160 x128 dots LCD |

| LG1602 | 制造商:AGERE 制造商全稱:AGERE 功能描述:LG1602 Decision Circuit |

| LG1602AXB | 制造商:AGERE 制造商全稱:AGERE 功能描述:LG1602 Decision Circuit |

| LG1602BXB | 制造商:AGERE 制造商全稱:AGERE 功能描述:LG1602 Decision Circuit |

| LG1605DXB | 制造商:AGERE 制造商全稱:AGERE 功能描述:LG1605DXB Limiting Amplifier |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。