- 您現在的位置:買賣IC網 > PDF目錄358795 > LH521028A (Sharp Corporation) CMOS 64K x 18 Static RAM PDF資料下載

參數資料

| 型號: | LH521028A |

| 廠商: | Sharp Corporation |

| 英文描述: | CMOS 64K x 18 Static RAM |

| 中文描述: | 64K的× 18的CMOS靜態(tài)RAM |

| 文件頁數: | 11/15頁 |

| 文件大小: | 124K |

| 代理商: | LH521028A |

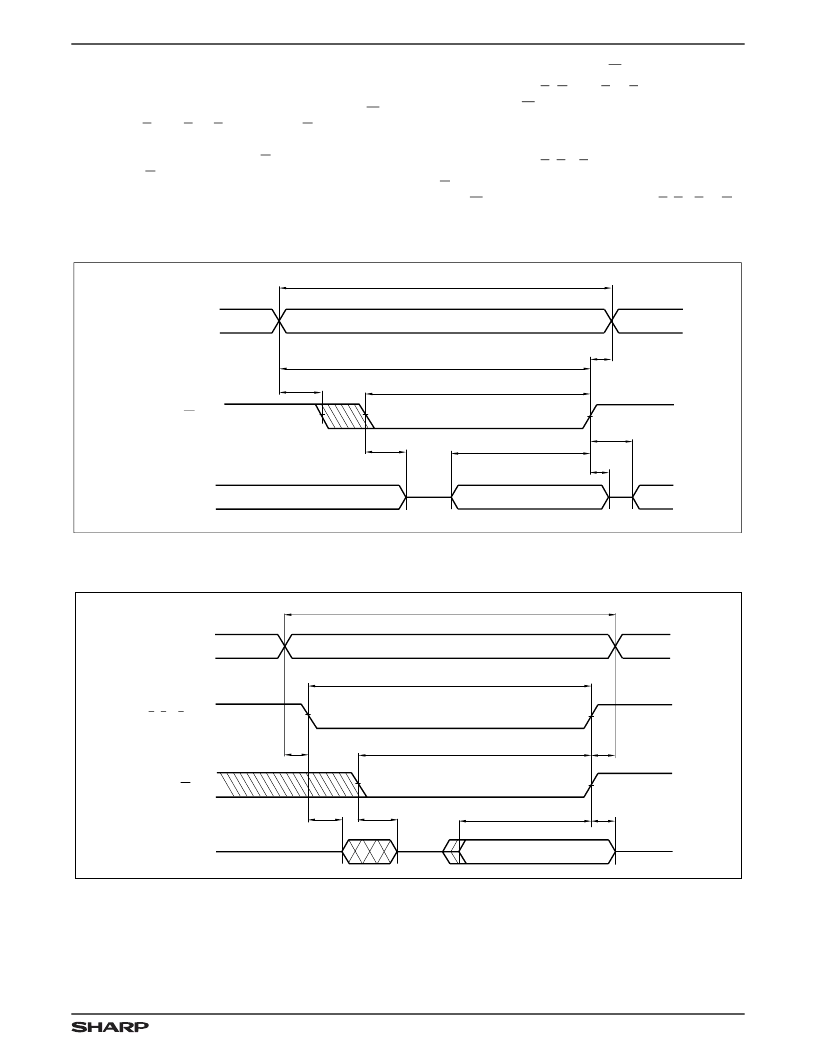

TIMING DIAGRAMS – WRITE CYCLE

Addresses must be stable during unlatched Write

cycles. The outputs will remain in the High-Z state if W is

LOW when E and S

H

/ S

L

go LOW. If G is HIGH, the

outputs will remain in the High-Z state. Although these

examples illustrate timing with G active, it is recom-

mended that G be held HIGH for all Write cycles. This will

prevent the LH521028’s outputs from becoming active,

preventing bus contention, thereby reducing system

noise.

Write Cycle No. 1 (Unlatched W Controlled Write)

Chip is selected: E, G, and S

H

/ S

L

are LOW, ALE is

High. Using only

W to control Write cycles may not offer

the best performance since both t

WHZ

and t

DW

timing

specifications must be met.

Write Cycle No. 2 (E, S

L

, S

H

Controlled Write)

G is LOW. DQ lines may transition to Low-Z if the falling

edge of W occurs after the falling edge of E, S

H

/S

L

if G is

LOW.

t

WC

t

AW

t

WP

t

DW

t

AH

t

WLZ

t

WHZ

t

AS

t

DH

PREVIOUS OUTPUT

VALID DATA

VALID ADDRESS

521028-6

W

ADDRESS

DQ

Figure 8. Write Cycle No. 1

t

EW

ADDRESS

E, S

L

, S

H

DQ

VALID DATA

VALID ADDRESS

t

WC

t

WP

t

AH

t

AS

t

ELZ

t

WHZ

t

DW

t

DH

W

521028-7

Figure 9. Write Cycle No. 2

CMOS 64K

×

18 Static RAM

LH521028A

11

相關PDF資料 |

PDF描述 |

|---|---|

| LH521028 | CMOS 64K x 18 Static RAM |

| LH52253K35 | CMOS 64K X 4 STATIC RAM |

| LH52256C-10LL | CMOS 256K (32K x8) Static RAM(CMOS 256K (32K x8) 靜態(tài)RAM) |

| LH52256CD-70LL | CMOS 256K (32K x8) Static RAM(CMOS 256K (32K x8) 靜態(tài)RAM) |

| LH52256CHN-70LL | CMOS 256K (32K x8) Static RAM(CMOS 256K (32K x8) 靜態(tài)RAM) |

相關代理商/技術參數 |

參數描述 |

|---|---|

| LH521028AU-15 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x18 SRAM |

| LH521028AU-17 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x18 SRAM |

| LH521028AU-20 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x18 SRAM |

| LH521028AU-25 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x18 SRAM |

| LH521028AU-35 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x18 SRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復。