- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄44112 > LK4601-9PT 1-OUTPUT 150 W AC-DC PWR FACTOR CORR MODULE PDF資料下載

參數(shù)資料

| 型號(hào): | LK4601-9PT |

| 元件分類: | 電源模塊 |

| 英文描述: | 1-OUTPUT 150 W AC-DC PWR FACTOR CORR MODULE |

| 封裝: | HEAT SINK, METAL, CASE K02, MODULE |

| 文件頁數(shù): | 17/28頁 |

| 文件大?。?/td> | 606K |

| 代理商: | LK4601-9PT |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁當(dāng)前第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁

Cassette Style

150 Watt AC-DC Converters

K Series PFC

Edition 01/01.2001

24/28

Vo1+

Vo1–

D

UD

ID

Rp

Input

11007

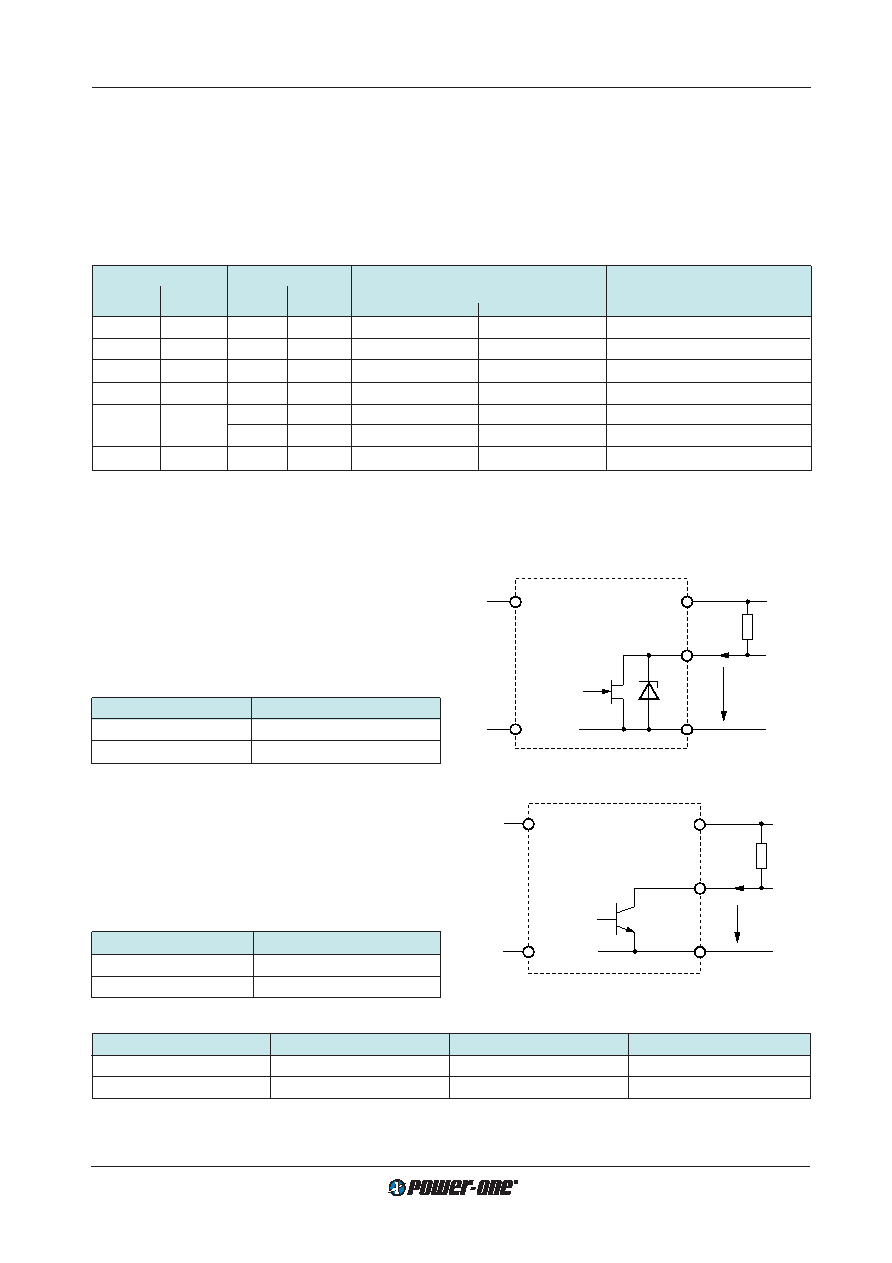

NPN output (D5...DD):

Connector pin D is internally connected via the collector-

emitter path of a NPN transistor to the negative potential of

output 1.

UD

< 0.4 V (logic low) corresponds to a monitored

voltage level (

Ui o1)

> U

t + Uh. The current ID

through the open collector should not exceed 20 mA. The

NPN output is not protected against external overvoltages.

UD should not exceed 40 V.

Ui, Uo1 status

D output,

UD

Ui or Uo1 < Ut

high, H,

ID ≤ 25 A at UD = 40 V

Ui and Uo1 > Ut + Uh

low, L,

UD ≤ 0.4 V at ID = 20 mA

Fig. 37

Option D5...DD: NPN output, Uo1

≤ 40 V, I

D

≤ 20 mA

Table 19: D-output logic signals

Version of D

Ui < Ut resp. Uo < Ut

Ui > Ut + Uh resp. Uo > Ut

Conguration

D1, D2, D3, D4, D0

low

high

JFET

D5, D6, D7, D8, D9, DD

high

low

NPN

Option D Undervoltage monitor

The input and/or output undervoltage monitoring circuit op-

erates independently of the built-in input undervoltage lock-

out circuit. A logic "low" (JFET output) or "high" signal (NPN

output) is generated at pin 20 as soon as one of the moni-

tored voltages drops below the preselected threshold level

Ut. The return for this signal is Vo1–. The D output reco-

vers when the monitored voltage(s) exceed(s)

Ut + Uh. The

Table 18: Undervoltage monitoring functions

Output type

Monitoring

Minimum adjustment range

Typical hysteresis

Uho [% of Ut]

JFET

NPN

U i

Uo1

of threshold level

U t

for

U t min...U t max

Uti

Uto

Uho

D1

D5

no

yes

-

3.5...40 V 1

2.5...0.6

D2

D6

yes

no

355 V DC 4

--

D3

D7

yes

355 V DC 4

(0.95...0.985

Uo1) 2

"0"

D4

D8

no

yes

-

(0.95...0.985

Uo1) 2

"0"

D0

D9

no

yes

-

3.5...40 V 3

2.5...0.6

yes

355 V DC 4

3.5...40 V 3

2.5...0.6

DD

yes

355 V DC4

3.5...40 V 1

2.5...0.6

1 Threshold level adjustable by potentiometer

2 Fixed value. Tracking if Uo1 adjusted via R-input, option P or sense lines.

3 The threshold level permanently adjusted according to customer specication

±2% at 25°C. Any value within the specied range is

basically possible but causes a special type designation in addition to the standard option designations (D0/D9)!

4 Option D monitors the boost regulator output voltage. The trigger level is adjusted in the factory to 355 V DC.

threshold level

Uti is adjusted in the factory. The threshold

level

Uto is either adjusted by a potentiometer, accessible

through a hole in the front cover, or factory adjusted to a

xed value specied by the customer.

Option D exists in various versions D0...DD as shown in the

following table.

Vo1+

Vo1–

D

UD

ID

Rp

Input

11006

Fig. 36

Option D0...D4: JFET output, ID

≤ 2.5 mA

JFET output (D0…D4):

Connector pin D is internally connected via the drain-

source path of a JFET (self-conducting type) to the nega-

tive potential of output 1.

UD

≤ 0.4 V (logic low) corresponds

to a monitored voltage level (

Ui and/or Uo1)

<U

t. The cur-

rent

ID through the JFET should not exceed 2.5 mA. The

JFET is protected by a 0.5 W Zener diode of 8.2 V against

external overvoltages.

Ui, Uo1 status

D output,

UD

Ui or Uo1 < Ut

low, L,

UD ≤ 0.4 V at ID = 2.5 mA

Ui and Uo1 > Ut + Uh

high, H,

ID ≤ 25 A at UD = 5.25 V

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LK5320-7EPD2T | 2-OUTPUT 150 W AC-DC PWR FACTOR CORR MODULE |

| LK5320-7EPD7TB1 | 2-OUTPUT 150 W AC-DC PWR FACTOR CORR MODULE |

| LK5320-7ER | 2-OUTPUT 150 W AC-DC PWR FACTOR CORR MODULE |

| LK5320-7RD8TB1 | 2-OUTPUT 150 W AC-DC PWR FACTOR CORR MODULE |

| LK5320-9PD0B1 | 2-OUTPUT 150 W AC-DC PWR FACTOR CORR MODULE |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LK4602-9ER-D8T-G16-K020C | 制造商:Power-One 功能描述:- Bulk |

| LK460D3LA29 | 制造商:Sharp Microelectronics Corporation 功能描述:46" (1920X1080) |

| LK460D3LZ19 | 制造商:Sharp Microelectronics Corporation 功能描述:46.0 inch 1920 x 1080 Digital Landscape CCFL TFT LCD Module |

| LK-470-001 | 功能描述:LED MODULE 1W BLUE RoHS:是 類別:光電元件 >> LED - 高亮度電源模塊 系列:- 標(biāo)準(zhǔn)包裝:36 系列:5027 TFFC STAR K2 顏色:暖白色 配置:星形 在特定電流下的光通量 - 測(cè)試:75lm 電流 - 測(cè)試:350mA 電流 - 最大:1.5A 帶連接器:無 驅(qū)動(dòng)器電路:無 波長(zhǎng):- 電壓:- |

| LK-470-001-FC | 功能描述:LED MODULE 1W BLUE W/CONN RoHS:是 類別:光電元件 >> LED - 高亮度電源模塊 系列:- 標(biāo)準(zhǔn)包裝:36 系列:5027 TFFC STAR K2 顏色:暖白色 配置:星形 在特定電流下的光通量 - 測(cè)試:75lm 電流 - 測(cè)試:350mA 電流 - 最大:1.5A 帶連接器:無 驅(qū)動(dòng)器電路:無 波長(zhǎng):- 電壓:- |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。