- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄358828 > LM2711 (National Semiconductor Corporation) TFT Panel Module PDF資料下載

參數(shù)資料

| 型號(hào): | LM2711 |

| 廠商: | National Semiconductor Corporation |

| 英文描述: | TFT Panel Module |

| 中文描述: | 液晶面板模塊 |

| 文件頁(yè)數(shù): | 16/20頁(yè) |

| 文件大小: | 846K |

| 代理商: | LM2711 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)當(dāng)前第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)

Operation

(Continued)

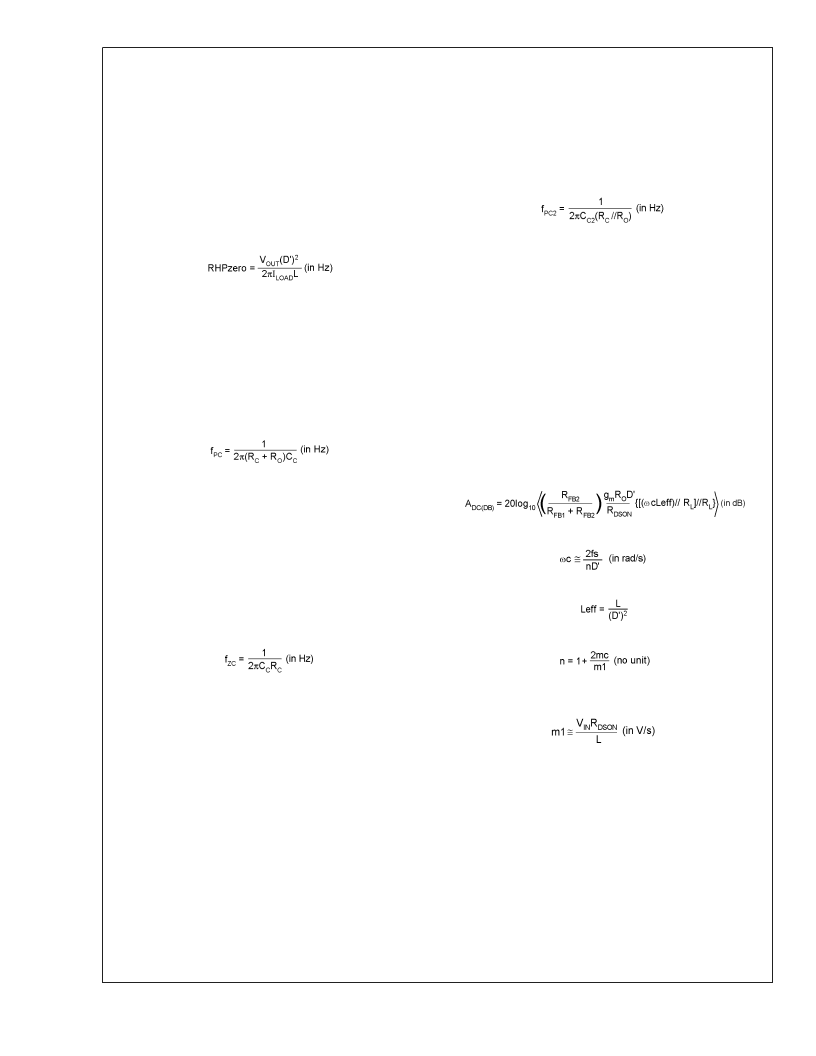

RIGHT HALF PLANE ZERO

A current mode control boost regulator has an inherent right

half plane zero (RHP zero). This zero has the effect of a zero

in the gain plot, causing an imposed +20dB/decade on the

rolloff, but has the effect of a pole in the phase, subtracting

another 90 in the phase plot. This can cause undesirable

effects if the control loop is influenced by this zero. To ensure

the RHP zero does not cause instability issues, the control

loop should be designed to have a bandwidth of less than

1

2

the frequency of the RHP zero. This zero occurs at a fre-

quency of:

where I

LOAD

is the maximum load current.

SELECTING THE COMPENSATION COMPONENTS

The first step in selecting the compensation components R

C

and C

is to set a dominant low frequency pole in the control

loop. Simply choose values for R

and C

C

within the ranges

given in the

Introduction to Compensation

section to set this

pole in the area of 10Hz to 500Hz. The frequency of the pole

created is determined by the equation:

where R

O

is the output impedance of the error amplifier,

approximately 1M

. Since R

C

is generally much less than

R

O

, it does not have much effect on the above equation and

can be neglected until a value is chosen to set the zero f

ZC

.

f

is created to cancel out the pole created by the output

capacitor, f

. The output capacitor pole will shift with differ-

ent load currents as shown by the equation, so setting the

zero is not exact. Determine the range of f

over the ex-

pected loads and then set the zero f

to a point approxi-

mately in the middle. The frequency of this zero is deter-

mined by:

Now R

C

can be chosen with the selected value for C

C

.

Check to make sure that the pole f

PC

is still in the 10Hz to

500Hz range, change each value slightly if needed to ensure

both component values are in the recommended range.After

checking the design at the end of this section, these values

can be changed a little more to optimize performance if

desired. This is best done in the lab on a bench, checking the

load step response with different values until the ringing and

overshoot on the output voltage at the edge of the load steps

is minimal. This should produce a stable, high performance

circuit. For improved transient response, higher values of R

C

should be chosen. This will improve the overall bandwidth

which makes the regulator respond more quickly to tran-

sients. If more detail is required, or the most optimal perfor-

mance is desired, refer to a more in depth discussion of

compensating current mode DC/DC switching regulators.

HIGH OUTPUT CAPACITOR ESR COMPENSATION

When using an output capacitor with a high ESR value, or

just to improve the overall phase margin of the control loop,

another pole may be introduced to cancel the zero created

by the ESR. This is accomplished by adding another capaci-

tor, C

, directly from the compensation pin V

to ground, in

parallel with the series combination of R

C

and C

C

. The pole

should be placed at the same frequency as f

Z1

, the ESR

zero. The equation for this pole follows:

To ensure this equation is valid, and that C

C2

can be used

without negatively impacting the effects of R

C

and C

C

, f

PC2

must be greater than 10f

ZC

.

CHECKING THE DESIGN

The final step is to check the design. This is to ensure a

bandwidth of

1

2

or less of the frequency of the RHP zero.

This is done by calculating the open-loop DC gain,A

.After

this value is known, you can calculate the crossover visually

by placing a 20dB/decade slope at each pole, and a +20dB/

decade slope for each zero. The point at which the gain plot

crosses unity gain, or 0dB, is the crossover frequency. If the

crossover frequency is less than

1

2

the RHP zero, the phase

margin should be high enough for stability. The phase mar-

gin can also be improved by adding C

C2

as discussed earlier

in the section. The equation for A

DC

is given below with

additional equations required for the calculation:

mc

)

0.072fs (in V/s)

where R

is the minimum load resistance, V

is the maxi-

mum input voltage, g

is the error amplifier transconduc-

tance found in the

Electrical Characteristics

table, and R

D-

SON

is the value chosen from the graph "R

vs. V

IN

" in

the

Typical Performance Characteristics

section.

BUFFER (Vcom and GMAx) COMPENSATION

The architecture used for the buffers in the LM2711 requires

external compensation on the output. Depending on the

equivalent capacitive load of the TFT-LCD panel, external

components at the buffer outputs may or may not be neces-

sary. If the capacitance presented by the load is equal to or

greater than 5nF no external components are needed as the

TFT-LCD panel will act as compensation itself. Distributed

resistive and capacitive loads enhance stability and increase

L

www.national.com

16

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LM2715MT-ADJ | TFT Panel Module |

| LM2715MTX-ADJ | TFT Panel Module |

| LM2715 | TFT Panel Module |

| LM2716MTX-ADJ | Dual (Step-up and Step-down) PWM DC/DC Converter |

| LM2716MT-ADJ | Dual (Step-up and Step-down) PWM DC/DC Converter |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LM2711A-ADJ WAF | 制造商:Texas Instruments 功能描述: |

| LM2711MT-ADJ | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:TFT Panel Module |

| LM2711MTX-ADJ | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:TFT Panel Module |

| LM2715 | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:TFT Panel Module |

| LM2715_06 | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:TFT Panel Module |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。