- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄358864 > LM41 (National Semiconductor Corporation) Hardware Monitor with Thermal Diode Inputs and SensorPath⑩ Bus PDF資料下載

參數(shù)資料

| 型號(hào): | LM41 |

| 廠商: | National Semiconductor Corporation |

| 英文描述: | Hardware Monitor with Thermal Diode Inputs and SensorPath⑩ Bus |

| 中文描述: | 硬件監(jiān)控與熱二極管輸入和SensorPath⑩巴士 |

| 文件頁(yè)數(shù): | 12/27頁(yè) |

| 文件大小: | 367K |

| 代理商: | LM41 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)當(dāng)前第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)

1.0 Functional Description

(Continued)

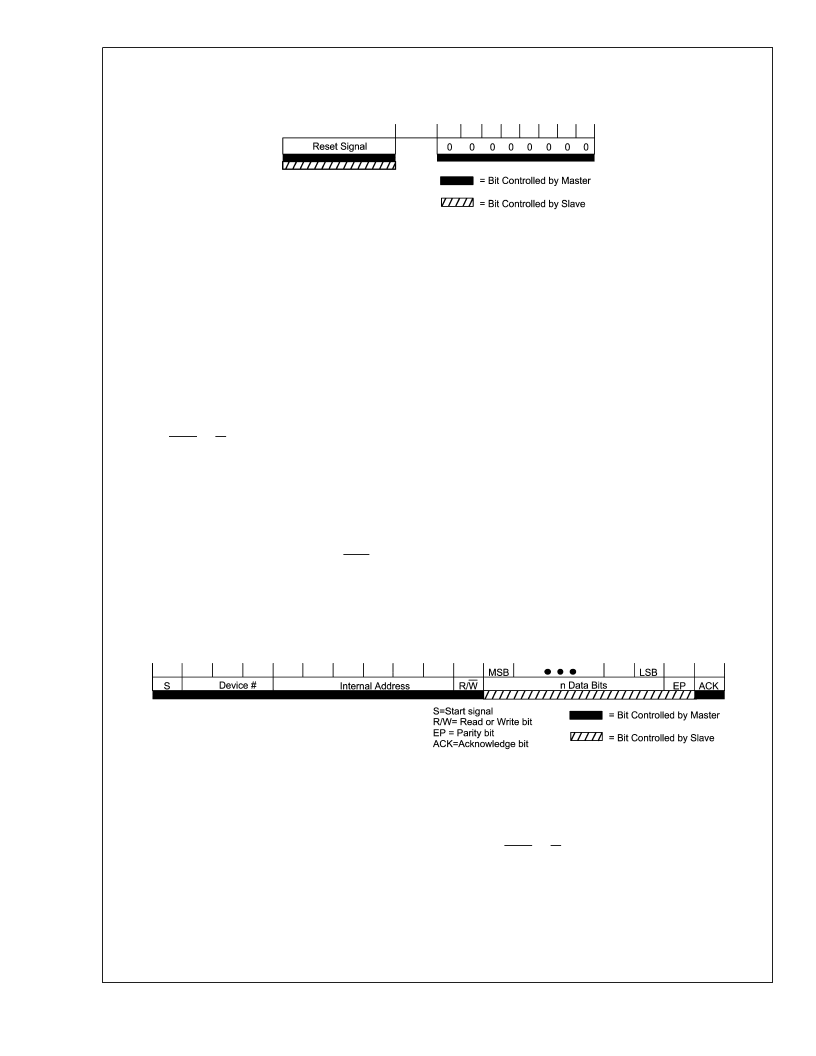

1.3.2 Read Transaction

During a read transaction, the master reads data from a

register at a specified address within a slave. A read trans-

action begins with a Start Bit and ends with an ACK bit, as

shown in

Figure 5

.

Device Number

This is the address of the LM41 device

accessed. Address "000" is a broadcast address and can

be responded to by all the slave devices. The LM41

ignores the broadcast address during a read transaction.

Internal Address

The address of a register within the

LM41 that is read.

Read/Write (R/W)

A "1" indicates a read transaction.

Data Bits

During a read transaction the data bits are

driven by the LM41. Data is transferred serially with the

most significant bit first. This allows throughput optimiza-

tion based on the information that needs to be read.

The LM41 supports 8-bit or 16-bit data fields, as de-

scribed in

Section 2.0

"Register Set".

Even Parity (EP)

This bit is based on all preceding bits

(device number, internal address, Read/Write and data

bits) and the parity bit itself. The parity -number of 1’s - of

all the preceding bits and the parity bit must be even - i.e.,

the result must be 0. During a read transaction, the EP bit

is sent by the LM41 to the master to allow the master to

check the received data before using it.

Acknowledge (ACK)

During a read transaction theACK

bit is sent by the master indicating that the EP bit was

received and was found to be correct, when compared to

the data preceding it, and that no conflict was detected

on the bus (excluding Attention Request - see

Section

1.3.5

"Attention Request Transaction"). A read transfer is

considered "complete" only when theACK bit is received.

A transaction that was not positively acknowledged is not

considered "complete" by the LM41 and following are

performed:

— The BER bit in the LM41 Device Status register is set

— The LM41 generates an Attention Request before, or

together with the Start Bit of the next transaction

A transaction that was not positively acknowledged is

also not considered "complete" by the master (i.e. inter-

nal operations related to the transaction are not per-

formed). The transaction may be repeated by the master,

after detecting the source of the Attention Request (the

LM41 that has a set BER bit in the Device Status regis-

ter). Note that the SensorPath protocol neither forces, nor

automates re-execution of the transaction by the master.

The values of the ACK bit are:

— 1: Data was received correctly

— 0: An error was detected (no-acknowledge).

1.3.3 Write Transaction

In a write transaction, the master writes data to a register at

a specified address in the LM41. A write transaction begins

with a Start Bit and ends with an ACK Data Bit, as show in

Figure 6

.

Device Number

This is the address of the slave device

accessed. Address "000" is a broadcast address and is

responded to by all the slave devices. The LM41 re-

sponds to broadcast messages to the Device Control

Register.

Internal Address

This is the register address in the

LM41 that will be written.

Read/Write (R/W)

A "0" data bit directs a write transac-

tion.

20070308

FIGURE 4. Bus Reset Transaction

20070309

FIGURE 5. Read Transaction, master reads data from LM41

L

www.national.com

12

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LM431AIBP | Adjustable Precision Zener Shunt Regulator |

| LM431CCML | Positive Adjustable Voltage Regulator |

| LM431CCMF | Positive Adjustable Voltage Regulator |

| LM431CCM3X | Positive Adjustable Voltage Regulator |

| LM431BIMX | Positive Adjustable Voltage Regulator |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LM411MH/883 | 制造商:NSC 功能描述:OP AMP TO-99 8 pin |

| LM411MH883 | 制造商:NSC 功能描述:OP AMP TO-99 8 pin |

| LM412 | 制造商:Pro-Signal 功能描述:LCD SCREEN 4" |

| LM4120 | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:Precision Micropower Low Dropout Voltage Reference |

| LM4120_05 | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:Precision Micropower Low Dropout Voltage Reference |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。