- 您現(xiàn)在的位置:買賣IC網 > PDF目錄358931 > LP62S16512-T (AMIC Technology Corporation) 512K X 16 BIT LOW VOLTAGE CMOS SRAM PDF資料下載

參數資料

| 型號: | LP62S16512-T |

| 廠商: | AMIC Technology Corporation |

| 英文描述: | 512K X 16 BIT LOW VOLTAGE CMOS SRAM |

| 中文描述: | 為512k × 16位低電壓CMOS的SRAM |

| 文件頁數: | 7/14頁 |

| 文件大?。?/td> | 150K |

| 代理商: | LP62S16512-T |

LP62S16512-I Series

PRELIMINARY

(March, 2002, Version 0.2)

7

AMIC Technology, Inc.

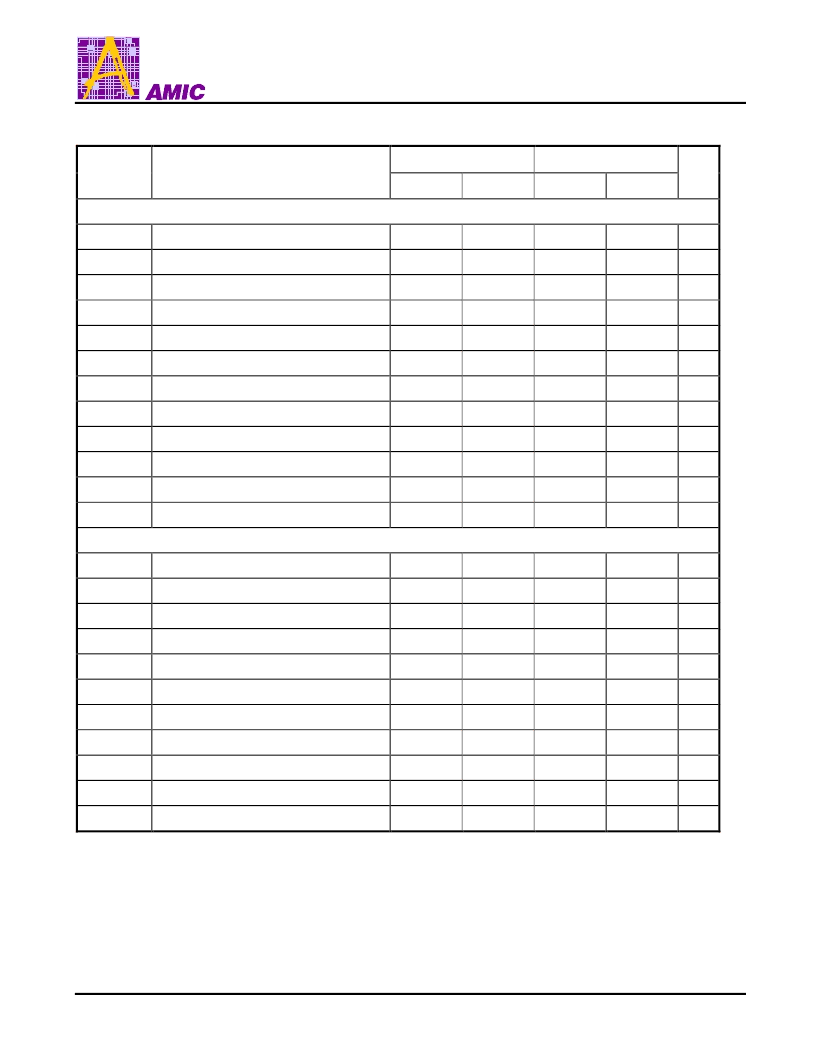

AC Characteristics

(T

A

= -40

°

C to +85

°

C, VCC = 2.7V to 3.6V)

Symbol

Parameter

LP62S16512-55LLI

LP62S16512-70LLI

Unit

Max.

Min.

Min.

Max.

Read Cycle

t

RC

Read Cycle Time

55

-

70

-

ns

t

AA

Address Access Time

-

55

-

70

ns

t

Acs1 ,

t

Acs2

Chip Enable Access Time

-

55

-

70

ns

t

BE

Byte Enable Access Time

-

55

-

70

ns

t

OE

Output Enable to Output Valid

-

25

-

35

ns

t

CLZ1 ,

t

CLZ2

Chip Enable to Output in Low Z

10

-

10

-

ns

t

BLZ

Byte Enable to Output in Low Z

10

-

10

-

ns

t

OLZ

Output Enable to Output in Low Z

5

-

5

-

ns

t

CHZ1 ,

t

CHZ2

Chip Disable to Output in High Z

-

20

-

25

ns

t

BHZ

Byte Disable to Output in High Z

-

20

-

25

ns

t

OHZ

Output Disable to Output in High Z

-

20

-

25

ns

t

OH

Output Hold from Address Change

5

-

5

-

ns

Write Cycle

t

WC

Write Cycle Time

55

-

70

-

ns

t

CW1 ,

t

CW2

Chip Enable to End of Write

50

-

60

-

ns

t

BW

Byte Enable to End of Write

50

-

60

-

ns

t

AS

Address Setup Time

0

-

0

-

ns

t

AW

Address Valid to End of Write

50

-

60

-

ns

t

WP

Write Pulse Width

40

-

50

-

ns

t

WR

Write Recovery Time

0

-

0

-

ns

t

WHZ

Write to Output in High Z

-

25

-

25

ns

t

DW

Data to Write Time Overlap

25

-

30

-

ns

t

DH

Data Hold from Write Time

0

-

0

-

ns

t

OW

Output Active from End of Write

5

-

5

-

ns

Note: t

CLZ1 ,

t

CLZ2 ,

t

BLZ

, t

OLZ

, t

CHZ1

, t

CHZ2 ,

t

BHZ

and t

OHZ

and t

WHZ

are defined as the time at which the outputs achieve the

open circuit condition and are not referred to output voltage levels.

相關PDF資料 |

PDF描述 |

|---|---|

| LP62S16512U-55LLI | Shielded Paired Cable; Number of Conductors:2; Conductor Size AWG:24; No. Strands x Strand Size:7 x 32; Jacket Material:Polyvinylchloride (PVC); Shielding Material:Aluminum Foil/Polyester Tape; Number of Pairs:1 RoHS Compliant: Yes |

| LP62S16512U-55LLT | Shielded Paired Cable; Number of Conductors:2; Conductor Size AWG:24; No. Strands x Strand Size:7 x 32; Jacket Material:Polyvinylchloride (PVC); Number of Pairs:1; Impedance:75ohm; Voltage Nom.:600V RoHS Compliant: Yes |

| LP62S16512U-70LLI | Shielded Paired Cable; Number of Conductors:2; Jacket Material:Polyvinylchloride (PVC); Number of Pairs:1; Leaded Process Compatible:Yes RoHS Compliant: Yes |

| LP62S16512U-70LLT | CABLE, 9502, 2PAIR, 30.5M; Cores, No. of:4; Conductor make-up:7/32AWG; Area, conductor CSA:0.2mm2; Diameter, External:5.64m; Material, secondary insulation:PVC; Length, Reel (Imperial):100ft; Colour, secondary insulation:Chrome; RoHS Compliant: Yes |

| LP62S1664CU-55LLI | 64K X 16 BIT LOW VOLTAGE CMOS SRAM |

相關代理商/技術參數 |

參數描述 |

|---|---|

| LP62S16512U-55LLI | 制造商:AMICC 制造商全稱:AMIC Technology 功能描述:512K X 16 BIT LOW VOLTAGE CMOS SRAM |

| LP62S16512U-55LLT | 制造商:AMICC 制造商全稱:AMIC Technology 功能描述:512K X 16 BIT LOW VOLTAGE CMOS SRAM |

| LP62S16512U-70LLI | 制造商:AMICC 制造商全稱:AMIC Technology 功能描述:512K X 16 BIT LOW VOLTAGE CMOS SRAM |

| LP62S16512U-70LLT | 制造商:AMICC 制造商全稱:AMIC Technology 功能描述:512K X 16 BIT LOW VOLTAGE CMOS SRAM |

| LP62S1664C | 制造商:AMICC 制造商全稱:AMIC Technology 功能描述:64K X 16 BIT LOW VOLTAGE CMOS SRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復。