- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄358934 > LPC47M14M-NC (SMSC Corporation) CAT5 MULTI 1X9 VIDEO DISTRIBUTION AMP PDF資料下載

參數(shù)資料

| 型號(hào): | LPC47M14M-NC |

| 廠商: | SMSC Corporation |

| 英文描述: | CAT5 MULTI 1X9 VIDEO DISTRIBUTION AMP |

| 中文描述: | 128引腳ENGANCED超級(jí)I / O與LPC接口和USB集線器控制器 |

| 文件頁(yè)數(shù): | 60/205頁(yè) |

| 文件大?。?/td> | 1219K |

| 代理商: | LPC47M14M-NC |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)當(dāng)前第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)第151頁(yè)第152頁(yè)第153頁(yè)第154頁(yè)第155頁(yè)第156頁(yè)第157頁(yè)第158頁(yè)第159頁(yè)第160頁(yè)第161頁(yè)第162頁(yè)第163頁(yè)第164頁(yè)第165頁(yè)第166頁(yè)第167頁(yè)第168頁(yè)第169頁(yè)第170頁(yè)第171頁(yè)第172頁(yè)第173頁(yè)第174頁(yè)第175頁(yè)第176頁(yè)第177頁(yè)第178頁(yè)第179頁(yè)第180頁(yè)第181頁(yè)第182頁(yè)第183頁(yè)第184頁(yè)第185頁(yè)第186頁(yè)第187頁(yè)第188頁(yè)第189頁(yè)第190頁(yè)第191頁(yè)第192頁(yè)第193頁(yè)第194頁(yè)第195頁(yè)第196頁(yè)第197頁(yè)第198頁(yè)第199頁(yè)第200頁(yè)第201頁(yè)第202頁(yè)第203頁(yè)第204頁(yè)第205頁(yè)

SMSC DS – LPC47M14X

Page 60

Rev. 05/02/2000

ENHANCED DUMPREG

The DUMPREG command is designed to support system run-time diagnostics and application software development

and debug. To accommodate the LOCK command and the enhanced PERPENDICULAR MODE command the eighth

byte of the DUMPREG command has been modified to contain the additional data from these two commands.

COMPATIBILITY

The LPC47M14x was designed with software compatibility in mind. It is a fully backwards- compatible solution with the

older generation 765A/B disk controllers. The FDC also implements on-board registers for compatibility with the PS/2, as

well as PC/AT and PC/XT, floppy disk controller subsystems. After a hardware reset of the FDC, all registers, functions

and enhancements default to a PC/AT, PS/2 or PS/2 Model 30 compatible operating mode, depending on how the

IDENT and MFM bits are configured by the system BIOS.

6.6

The LPC47M14x incorporates two full function UARTs. They are compatible with the NS16450, the 16450 ACE

registers and the NS16C550A. The UARTs perform serial-to-parallel conversion on received characters and parallel-to-

serial conversion on transmit characters. The data rates are independently programmable from 460.8K baud down to

50 baud. The character options are programmable for 1 start; 1, 1.5 or 2 stop bits; even, odd, sticky or no parity; and

prioritized interrupts. The UARTs each contain a programmable baud rate generator that is capable of dividing the input

clock or crystal by a number from 1 to 65535. The UARTs are also capable of supporting the MIDI data rate. Refer to

the Configuration Registers for information on disabling, power down and changing the base address of the UARTs.

The interrupt from a UART is enabled by programming OUT2 of that UART to a logic "1". OUT2 being a logic "0"

disables that UARTs interrupt. The second UART also supports IrDA, HP-SIR and ASK-IR modes of operation.

Note:

The UARTs 1 and 2 may be configured to share an interrupt. Refer to the Configuration section for more

information.

REGISTER DESCRIPTION

Addressing of the accessible registers of the Serial Port is shown below. The base addresses of the serial ports are

defined by the configuration registers (see “Configuration” section). The Serial Port registers are located at sequentially

increasing addresses above these base addresses. The LPC47M14x contains two serial ports, each of which contain a

register set as described below.

SERIAL PORT (UART)

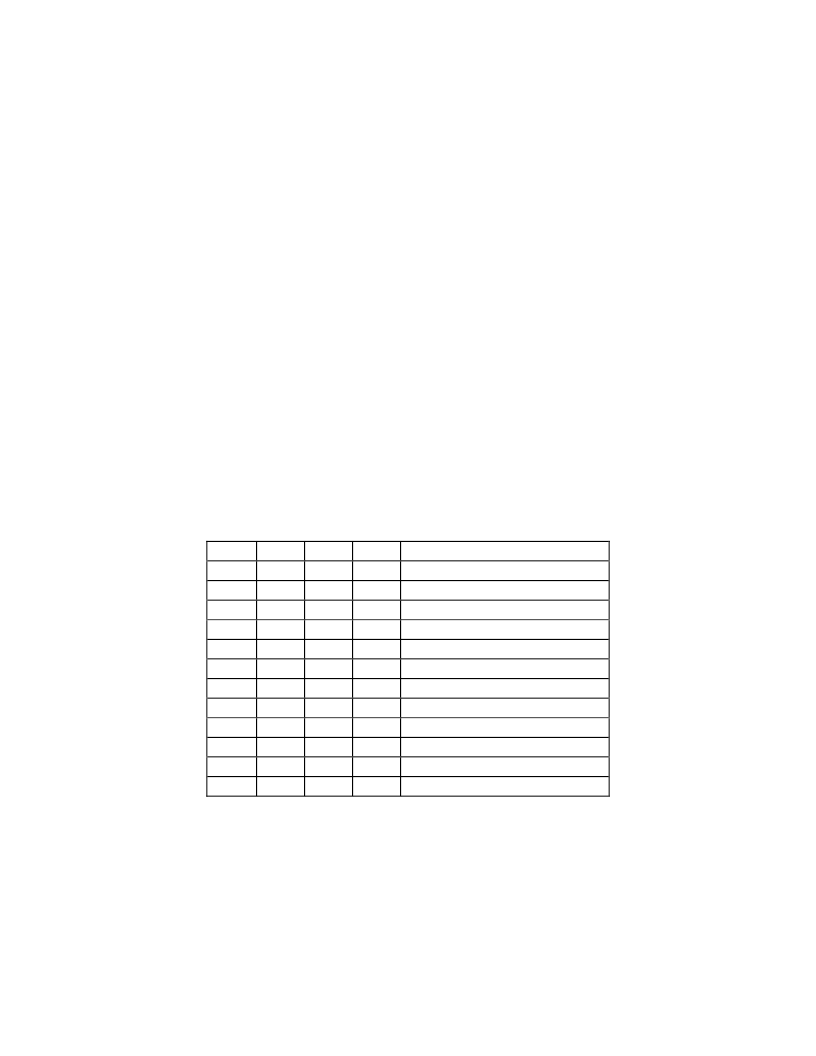

Table 29 – Addressing the Serial Port

DLAB*

A2

A1

A0

REGISTER NAME

0

0

0

0

Receive Buffer (read)

0

0

0

0

Transmit Buffer (write)

0

0

0

1

Interrupt Enable (read/write)

X

0

1

0

Interrupt Identification (read)

X

0

1

0

FIFO Control (write)

X

0

1

1

Line Control (read/write)

X

1

0

0

Modem Control (read/write)

X

1

0

1

Line Status (read/write)

X

1

1

0

Modem Status (read/write)

X

1

1

1

Scratchpad (read/write)

1

0

0

0

Divisor LSB (read/write)

1

0

0

1

Divisor MSB (read/write

*

Note:

DLAB is Bit 7 of the Line Control Register

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LPC47M14Q-NC | HD VIEW RECEIVER 2 PORT DAISYCHAINABLE |

| LPC47M14V-NC | AT PRINTER SERIAL CBL DB9 FEMALE - DB25 MALE |

| LPC47M14R-NC | 128 PIN ENGANCED SUPER I/O CONTROLLER WITH AN LPC INTERFACE AND USB HUB |

| LPC47M14I-NC | 128 PIN ENGANCED SUPER I/O CONTROLLER WITH AN LPC INTERFACE AND USB HUB |

| LPC47M14K-NC | RESTR 1.50K 1 TOL 1/8W MF |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LPC47M14N-NC | 制造商:SMSC 制造商全稱:SMSC 功能描述:128 PIN ENGANCED SUPER I/O CONTROLLER WITH AN LPC INTERFACE AND USB HUB |

| LPC47M14O-NC | 制造商:SMSC 制造商全稱:SMSC 功能描述:128 PIN ENGANCED SUPER I/O CONTROLLER WITH AN LPC INTERFACE AND USB HUB |

| LPC47M14P-NC | 制造商:SMSC 制造商全稱:SMSC 功能描述:128 PIN ENGANCED SUPER I/O CONTROLLER WITH AN LPC INTERFACE AND USB HUB |

| LPC47M14Q-NC | 制造商:SMSC 制造商全稱:SMSC 功能描述:128 PIN ENGANCED SUPER I/O CONTROLLER WITH AN LPC INTERFACE AND USB HUB |

| LPC47M14R-NC | 制造商:SMSC 制造商全稱:SMSC 功能描述:128 PIN ENGANCED SUPER I/O CONTROLLER WITH AN LPC INTERFACE AND USB HUB |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。