- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377667 > LT1011 (Linear Technology Corporation) Voltage Comparator PDF資料下載

參數(shù)資料

| 型號(hào): | LT1011 |

| 廠商: | Linear Technology Corporation |

| 英文描述: | Voltage Comparator |

| 中文描述: | 電壓比較器 |

| 文件頁(yè)數(shù): | 15/16頁(yè) |

| 文件大小: | 205K |

| 代理商: | LT1011 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)當(dāng)前第15頁(yè)第16頁(yè)

15

LT1011/LT1011A

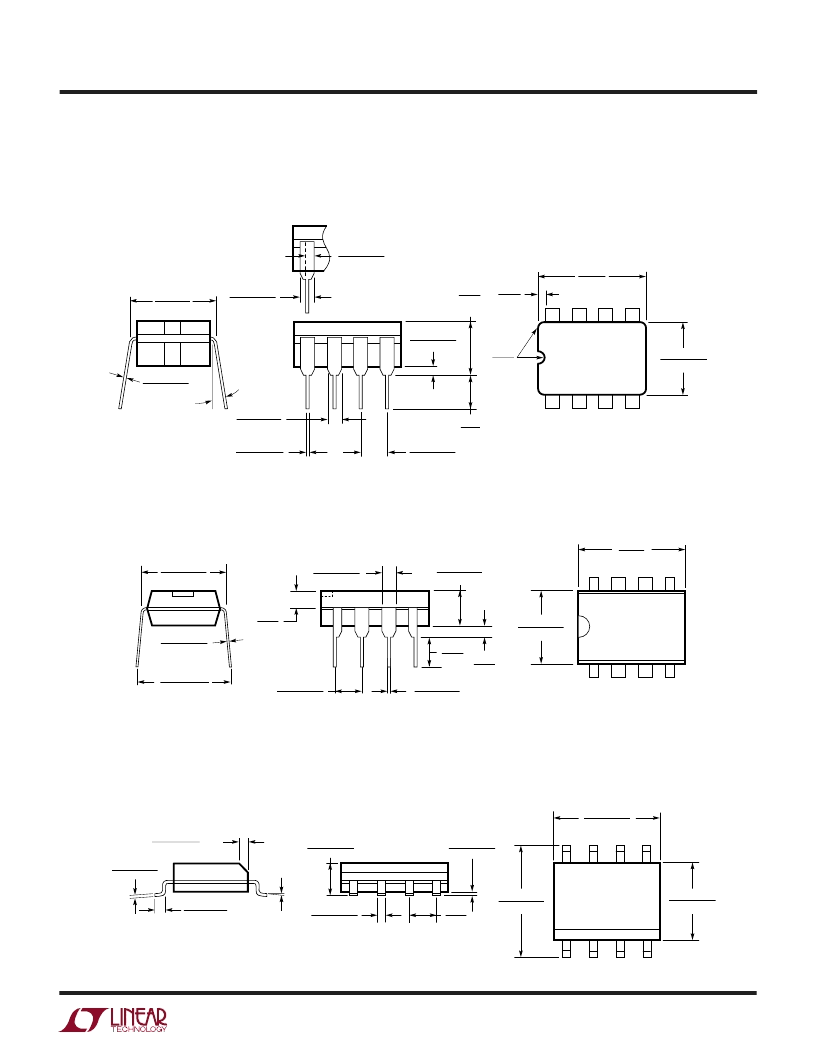

PACKAGE DESCRIPTIO

N

U

Dimensions in inches (millimeters) unless otherwise noted.

N8 Package

8-Lead PDIP (Narrow 0.300)

(LTC DWG # 05-08-1510)

S8 Package

8-Lead Plastic Small Outline (Narrow 0.150)

(LTC DWG # 05-08-1610)

J8 Package

8-Lead CERDIP (Narrow 0.300, Hermetic)

(LTC DWG # 05-08-1110)

J8 1197

0.014 – 0.026

(0.360 – 0.660)

0.200

(5.080)

MAX

0.015 – 0.060

(0.381 – 1.524)

0.125

3.175

MIN

0.100

±

0.010

(2.540

±

0.254)

0.300 BSC

(0.762 BSC)

0.008 – 0.018

(0.203 – 0.457)

0

°

– 15

°

0.045 – 0.068

(1.143 – 1.727)

0.045 – 0.068

(1.143 – 1.727)

FULL LEAD

OPTION

0.023 – 0.045

(0.584 – 1.143)

HALF LEAD

OPTION

CORNER LEADS OPTION

(4 PLCS)

0.005

(0.127)

MIN

0.405

(10.287)

MAX

0.220 – 0.310

(5.588 – 7.874)

1

2

3

4

8

7

6

5

0.025

(0.635)

RAD TYP

NOTE: LEAD DIMENSIONS APPLY TO SOLDER DIP/PLATE

OR TIN PLATE LEADS

N8 1197

0.100

±

0.010

(2.540

±

0.254)

0.065

(1.651)

TYP

0.045 – 0.065

(1.143 – 1.651)

0.130

±

0.005

(3.302

±

0.127)

0.020

(0.508)

MIN

0.018

±

0.003

(0.457

±

0.076)

0.125

(3.175)

MIN

0.009 – 0.015

(0.229 – 0.381)

0.300 – 0.325

(7.620 – 8.255)

0.325–0.015

+0.889

–0.381

8.255

(

)

1

2

3

4

8

7

6

5

0.255

±

0.015*

(6.477

±

0.381)

0.400*

(10.160)

MAX

*THESE DIMENSIONS DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS.

MOLD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.010 INCH (0.254mm)

1

2

3

4

0.150 – 0.157**

(3.810 – 3.988)

8

7

6

5

0.189 – 0.197*

(4.801 – 5.004)

0.228 – 0.244

(5.791 – 6.197)

0.016 – 0.050

0.406 – 1.270

0.010 – 0.020

(0.254 – 0.508)

×

45

°

0

°

– 8

°

TYP

0.008 – 0.010

(0.203 – 0.254)

SO8 0996

0.053 – 0.069

(1.346 – 1.752)

0.014 – 0.019

(0.355 – 0.483)

0.004 – 0.010

(0.101 – 0.254)

0.050

(1.270)

TYP

DIMENSION DOES NOT INCLUDE MOLD FLASH. MOLD FLASH

SHALL NOT EXCEED 0.006" (0.152mm) PER SIDE

DIMENSION DOES NOT INCLUDE INTERLEAD FLASH. INTERLEAD

FLASH SHALL NOT EXCEED 0.010" (0.254mm) PER SIDE

*

**

Information furnished by Linear Technology Corporation is believed to be accurate and reliable.

However, no responsibility is assumed for its use. Linear Technology Corporation makes no represen-

tation that the interconnection of its circuits as described herein will not infringe on existing patent rights.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LT1011A | Voltage Comparator |

| LT1011ACH | Voltage Comparator |

| LT1011ACN8 | Voltage Comparator |

| LT1011AMH | Counter Display Panel; Number of Digits/Alpha:6 |

| LT1011AMJ8 | Voltage Comparator |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LT1011A | 制造商:LINER 制造商全稱:Linear Technology 功能描述:Voltage Comparator |

| LT1011ACH | 制造商:LINER 制造商全稱:Linear Technology 功能描述:Voltage Comparator |

| LT1011ACJ8 | 制造商:Linear Technology 功能描述:Comparator Single ±15V/30V 8-Pin CDIP |

| LT1011ACJG | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| LT1011ACL | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Analog Comparator |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。