- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄39412 > LTC2161CUK#PBF (LINEAR TECHNOLOGY CORP) 1-CH 16-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PQCC48 PDF資料下載

參數(shù)資料

| 型號: | LTC2161CUK#PBF |

| 廠商: | LINEAR TECHNOLOGY CORP |

| 元件分類: | ADC |

| 英文描述: | 1-CH 16-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PQCC48 |

| 封裝: | 7 X 7 MM, LEAD FREE, PLASTIC, MO-220WKKD-2, QFN-48 |

| 文件頁數(shù): | 34/36頁 |

| 文件大?。?/td> | 651K |

| 代理商: | LTC2161CUK#PBF |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁當(dāng)前第34頁第35頁第36頁

LTC2162/LTC2161/LTC2160

7

216210f

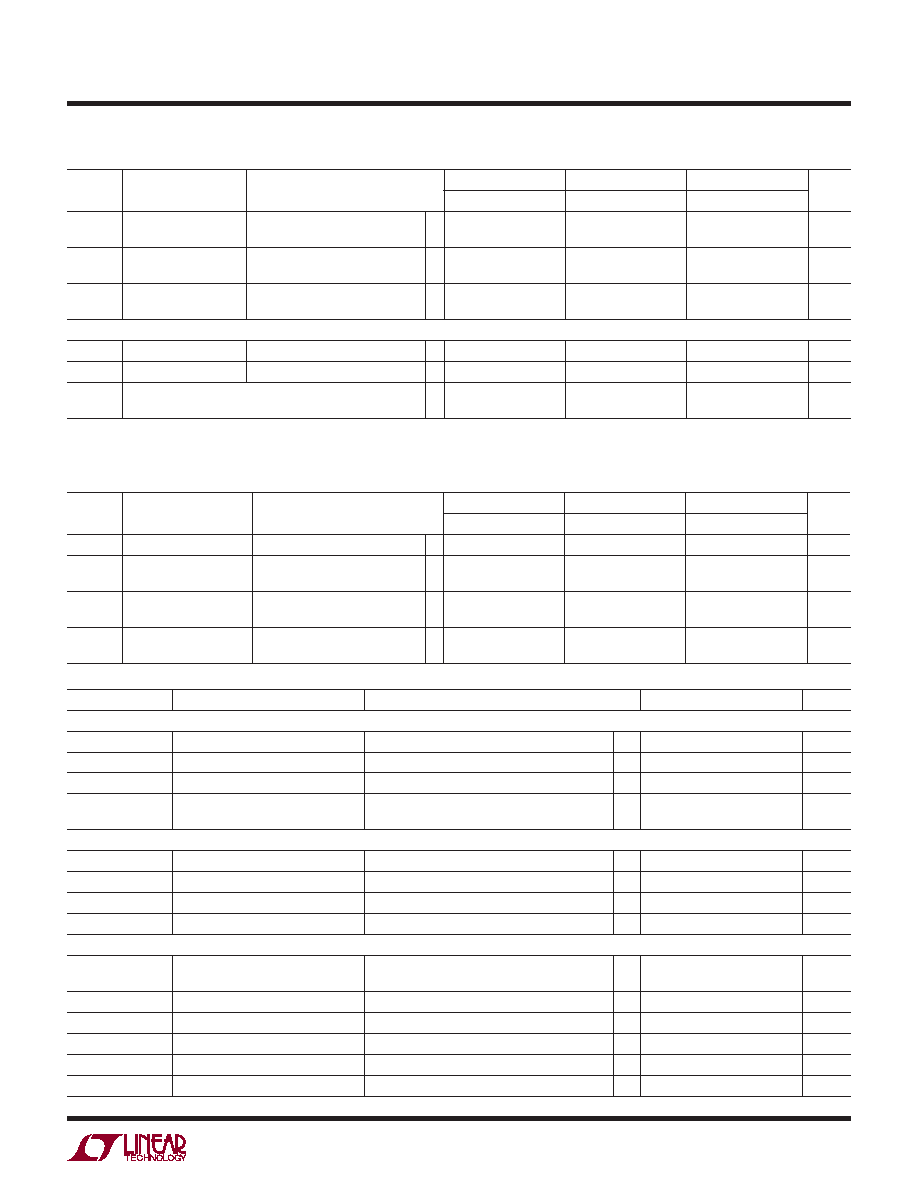

SYMBOL PARAMETER

CONDITIONS

LTC2162

LTC2161

LTC2160

UNITS

MIN

TYP

MAX

MIN

TYP

MAX

MIN

TYP

MAX

IVDD

Analog Supply Current Sine Wave Input 1.75mA Mode

3.5mA Mode l

50.3

51.1

57

37.3

38.2

42

26.8

27.7

31

mA

IOVDD

Digital Supply Current

(OVDD = 1.8V)

Sine Wave Input 1.75mA Mode

3.5mA Mode l

21.5

41.2

46

21.4

41.1

46

21.1

40.9

46

mA

PDISS

Power Dissipation

Sine Wave Input, 1.75mA Mode

Sine Wave Input, 3.5mA Mode

l

129

166

186

106

143

159

86

123

139

mW

All Output Modes

PSLEEP

Sleep Mode Power

1

mW

PNAP

Nap Mode Power

10

mW

PDIFFCLK Power Increase with Differential Encode Mode Enabled

(No Increase for Nap or Sleep Modes)

20

mW

power requireMenTs The

l

denotes the specifications which apply over the full operating temperature

range, otherwise specifications are at TA = 25°C. (Note 9)

TiMing characTerisTics The

l

denotes the specifications which apply over the full operating temperature

range, otherwise specifications are at TA = 25°C. (Note 5)

SYMBOL PARAMETER

CONDITIONS

LTC2162

LTC2161

LTC2160

UNITS

MIN

TYP

MAX

MIN

TYP

MAX

MIN

TYP

MAX

fS

Sampling Frequency

(Note 10)

l

1

65

1

40

1

25

MHz

tL

ENC Low Time (Note 8) Duty Cycle Stabilizer Off

Duty Cycle Stabilizer On

l

7.3

2

7.69

500

11.88

2

12.5

500

19

2

20

500

ns

tH

ENC High Time (Note 8) Duty Cycle Stabilizer Off

Duty Cycle Stabilizer On

l

7.3

2

7.69

500

11.88

2

12.5

500

19

2

20

500

ns

tAP

Sample-and-Hold

Acquisition Delay Time

0

ns

SYMBOL

PARAMETER

CONDITIONS

MIN

TYP

MAX

UNITS

DIGITAL DATA OUTPUTS (CMOS MODES: FULL DATA RATE AND DOUBLE DATA RATE)

tD

ENC to Data Delay

CL = 5pF (Note 8)

l

1.1

1.7

3.1

ns

tC

ENC to CLKOUT Delay

CL = 5pF (Note 8)

l

1

1.4

2.6

ns

tSKEW

DATA to CLKOUT Skew

tD – tC (Note 8)

l

0

0.3

0.6

ns

Pipeline Latency

Full Data Rate Mode

Double Data Rate Mode

6

6.5

Cycles

DIGITAL DATA OUTPUTS (LVDS MODE)

tD

ENC to Data Delay

CL = 5pF (Note 8)

l

1.1

1.8

3.2

ns

tC

ENC to CLKOUT Delay

CL = 5pF (Note 8)

l

1

1.5

2.7

ns

tSKEW

DATA to CLKOUT Skew

tD – tC (Note 8)

l

0

0.3

0.6

ns

Pipeline Latency

6.5

Cycles

SPI PORT TIMING (Note 8)

tSCK

SCK Period

Write Mode

Readback Mode, CSDO = 20pF, RPULLUP = 2k

l

40

250

ns

tS

CS to SCK Setup Time

l

5

ns

tH

SCK to CS Setup Time

l

5

ns

tDS

SDI Setup Time

l

5

ns

tDH

SDI Hold Time

l

5

ns

tDO

SCK Falling to SDO Valid

Readback Mode, CSDO = 20pF, RPULLUP = 2k

l

125

ns

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LTC2164CUK#TRPBF | 1-CH 16-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PQCC48 |

| LTC2164IUK#PBF | 1-CH 16-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PQCC48 |

| LTC2163CUK#TRPBF | 1-CH 16-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PQCC48 |

| LTC2163IUK#TRPBF | 1-CH 16-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PQCC48 |

| LTC2164CUK#PBF | 1-CH 16-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PQCC48 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LTC2161IUK#PBF | 制造商:Linear Technology 功能描述:ADC Single 40Msps 16-bit Parallel/Serial (SPI)/LVDS 48-Pin QFN EP 制造商:Linear Technology 功能描述:IC ADC 16BIT 40 MSPS 48-QFN |

| LTC2161IUK#TRPBF | 制造商:Linear Technology 功能描述:ADC Single 40Msps 16-bit Parallel/Serial (SPI)/LVDS 48-Pin QFN EP T/R 制造商:Linear Technology 功能描述:IC ADC 16BIT 40 MSPS 48-QFN |

| LTC2162 | 制造商:LINER 制造商全稱:Linear Technology 功能描述:Precision, Low Power Rail-to-Rail Input/Output |

| LTC2162-14 | 制造商:LINER 制造商全稱:Linear Technology 功能描述:High Linearity Differential RF/IF Amplifier/ADC Driver |

| LTC2162CUK#PBF | 制造商:Linear Technology 功能描述:ADC Single 65Msps 16-bit Parallel/Serial (SPI)/LVDS 48-Pin QFN EP 制造商:Linear Technology 功能描述:IC ADC 16BIT 65 MSPS 48-QFN 制造商:Linear Technology 功能描述:ADC 16BIT 65MSPS 48QFN 制造商:Linear Technology 功能描述:ADC, 16BIT, 65MSPS, 48QFN |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。