- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377801 > M13S128168A-6BG (ELITE SEMICONDUCTOR MEMORY TECHNOLOGY INC) 2M x 16 Bit x 4 Banks Double Data Rate SDRAM PDF資料下載

參數(shù)資料

| 型號: | M13S128168A-6BG |

| 廠商: | ELITE SEMICONDUCTOR MEMORY TECHNOLOGY INC |

| 元件分類: | DRAM |

| 英文描述: | 2M x 16 Bit x 4 Banks Double Data Rate SDRAM |

| 中文描述: | 8M X 16 DDR DRAM, 0.7 ns, PBGA60 |

| 封裝: | 8 X 13 MM, LEAD FREE, BGA-60 |

| 文件頁數(shù): | 27/49頁 |

| 文件大小: | 1513K |

| 代理商: | M13S128168A-6BG |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁當前第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁

ES MT

M13S128168A

Elite Semiconductor Memory Technology Inc.

Publication Date : Jun. 2007

Revision : 1.8 27/49

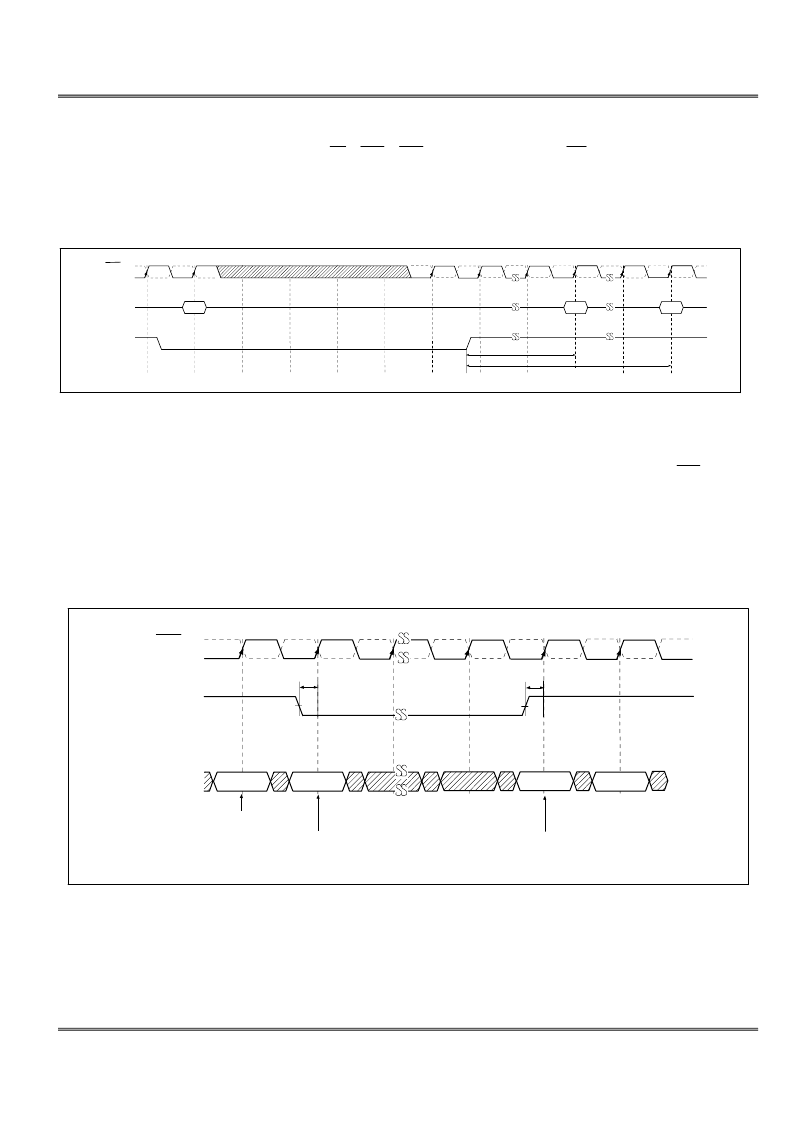

Self Refresh

A self refresh command is defines by having CS , RAS , CAS and CKE held low with

WE

high at the rising edge of the

clock (CLK). Once the self refresh command is initiated, CKE must be held low to keep the device in self refresh mode. During the

self refresh operation, all inputs except CKE are ignored. The clock is internally disabled during self refresh operation to reduce

power consumption. The self refresh is exited by supplying stable clock input before returning CKE high, asserting deselect or NOP

command and then asserting CKE high for longer than t

XSRD

for locking of DLL.

C L K

C L K

Power down

Power down is entered when CKE is registered low (no accesses can be in progress). If power-down occurs when all banks are

idle, this mode is referred to as precharge power-down; if power-down occurs when there is a row active in any bank, this mode is

referred to as active power-down. Entering power-down deactivates the input and output buffers, excluding CLK, CLK and CKE.

For maximum power savings, the user has the option of disabling the DLL prior to entering power-down. In that case, the DLL must

be enabled after exiting power-down, and 200 clock cycles must occur before a READ command can be issued. However,

power-down duration is limited by the refresh requirements of the device, so in most applications, the self-refresh mode is preferred

over the DLL disable power-down mode. In the power-down, CKE LOW and a stable clock signal must be maintained at the inputs

of the DDR SDRAM, and all other input signals are “Don’t Care”. The power-down state is synchronously exited when CKE is

registered HIGH (along with a NOP or DESELECT command). A valid executable command may be applied one clock cycle later.

CO MM AN D

CKE

t

X S N R

RSelf

RAuto

Read

t

X S R D

CO M M AN D

CKE

C L K

C L K

VALID

NOP

NOP

VALID

Enter power-down

mode

No column

acess

in program

t

IS

t

IS

Exit power-down

mode

相關PDF資料 |

PDF描述 |

|---|---|

| M13S128168A-6T | 2M x 16 Bit x 4 Banks Double Data Rate SDRAM |

| M13S128168A-6TG | 2M x 16 Bit x 4 Banks Double Data Rate SDRAM |

| M13S128168A-7.5AB | 2M x 16 Bit x 4 Banks Double Data Rate SDRAM |

| M13S128324A | 1M x 32 Bit x 4 Banks Double Data Rate SDRAM |

| M13S2561616A | 4M x 16 Bit x 4 Banks Double Data Rate SDRAM |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| M13S128168A-6BIG | 制造商:ESMT 制造商全稱:Elite Semiconductor Memory Technology Inc. 功能描述:2M x 16 Bit x 4 Banks Double Data Rate SDRAM |

| M13S128168A-6T | 制造商:ESMT 制造商全稱:Elite Semiconductor Memory Technology Inc. 功能描述:2M x 16 Bit x 4 Banks Double Data Rate SDRAM |

| M13S128168A-6TG | 制造商:ESMT 制造商全稱:Elite Semiconductor Memory Technology Inc. 功能描述:2M x 16 Bit x 4 Banks Double Data Rate SDRAM |

| M13S128168A-6TIG | 制造商:ESMT 制造商全稱:Elite Semiconductor Memory Technology Inc. 功能描述:2M x 16 Bit x 4 Banks Double Data Rate SDRAM |

| M13S128168A-7.5AB | 制造商:ESMT 制造商全稱:Elite Semiconductor Memory Technology Inc. 功能描述:2M x 16 Bit x 4 Banks Double Data Rate SDRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復。