- 您現在的位置:買賣IC網 > PDF目錄4472 > M1A3P1000L-1FGG484 (Microsemi SoC)IC FPGA M1 1KB FLASH 1M 484FBGA PDF資料下載

參數資料

| 型號: | M1A3P1000L-1FGG484 |

| 廠商: | Microsemi SoC |

| 文件頁數: | 10/12頁 |

| 文件大小: | 0K |

| 描述: | IC FPGA M1 1KB FLASH 1M 484FBGA |

| 標準包裝: | 40 |

| 系列: | ProASIC3L |

| RAM 位總計: | 147456 |

| 輸入/輸出數: | 300 |

| 門數: | 1000000 |

| 電源電壓: | 1.14V ~ 1.575 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 70°C |

| 封裝/外殼: | 484-BGA |

| 供應商設備封裝: | 484-FPBGA(23x23) |

ARM CortexTM-M1

Prod uct Br ief

7

For example:

Bytes 0–3 hold the first stored word

Bytes 4–7 hold the second stored word

The processor accesses data and code words in little-

endian format. Little-endian is the default memory

format for ARM processors.

In little-endian format, the byte with the lowest address

in a word is the least significant byte of the word. The

byte with the highest address in a word is the most

significant. The byte at address 0 of the memory system

connects to data lines 7–0.

Exceptions

The processor and the Nested Vectored Interrupt

Controller (NVIC) prioritize and handle all exceptions. All

exceptions are handled in Handler mode. Processor state

is automatically stored to the stack on an exception, and

automatically restored from the stack at the end of the

exception handler Interrupt Service Routine (ISR). The

following

features

enable

efficient,

low-latency

exception handling:

Automatic

state

saving

and

restoring.

The

processor pushes state registers on the stack

before entering the ISR, and pops them after

exiting the ISR with no instruction overhead.

Automatic reading of the vector table entry that

contains the ISR address in code memory or data

SRAM

Closely-coupled interface between the processor

and the NVIC to enable early processing of

interrupts

and

processing

of

late-arriving

interrupts with higher priority

Fixed number of interrupt priorities, from 2 bits, 4

levels

Separate stacks for Handler and Thread modes if

OS extensions are implemented

ISR control transfer using the calling conventions

of the C/C++ standard Procedure Call Standard for

the ARM Architecture (PCSAA)

Priority masking to support critical regions

Exception Types

Various types of exceptions exist in the processor. A fault

is an exception that results from an error condition.

Faults can be reported synchronously or asynchronously

to the instruction that caused them. In general, faults are

reported synchronously. Faults caused by writes over the

bus are asynchronous faults. A synchronous fault is

always reported with the instruction that caused the

fault. An asynchronous fault does not guarantee how it

is reported with respect to the instruction that caused

the fault. See Table 3 for a list and description of the

exceptions supported by ARM Cortex-M1

.

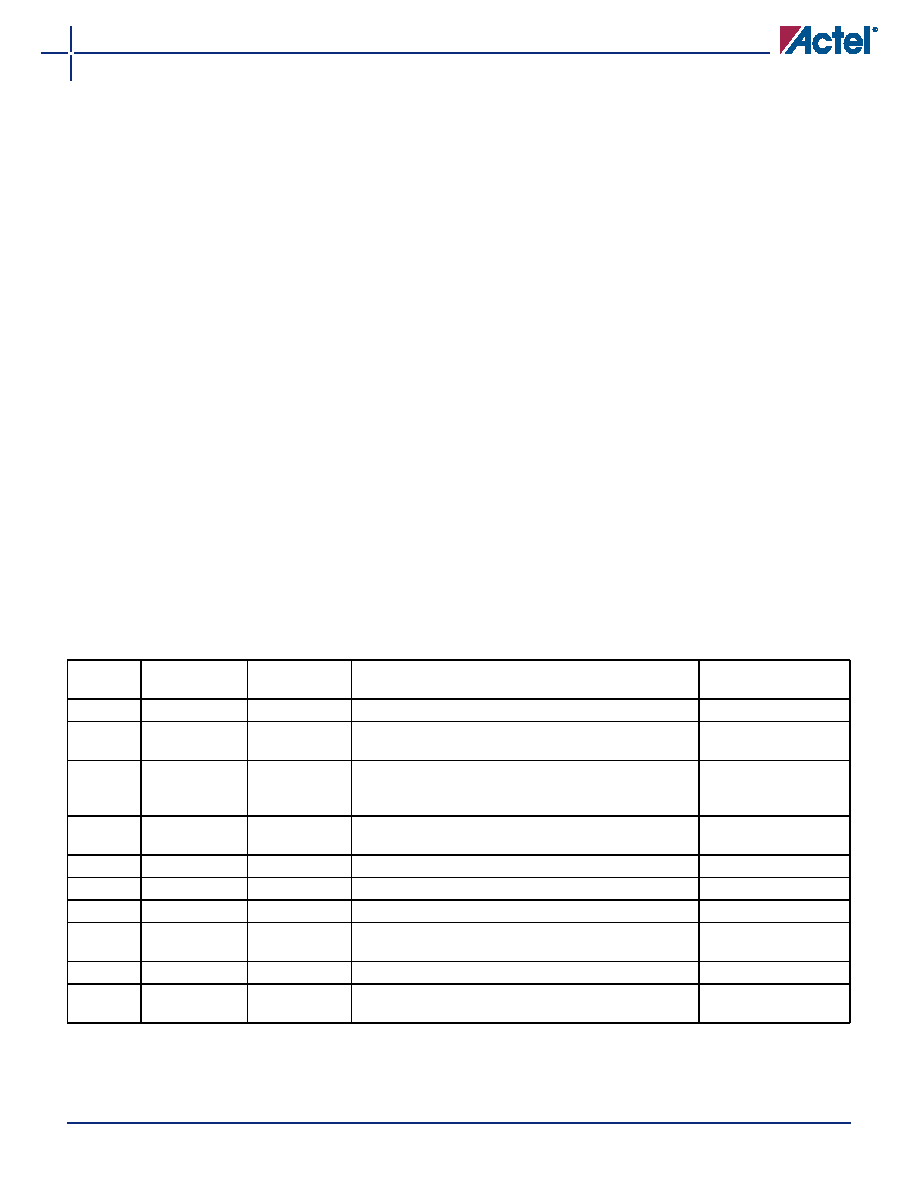

Table 3

Exception Types

Position

Exception

Type

Priority

Description

Activated

–

Stack top is loaded from first entry of vector table on Reset.

–

1

Reset

–3 (highest)

Invoked on power-up and warm Reset. On first instruction,

drops to lowest priority. Thread mode.

Asynchronous

2

Non-maskable

–2

Cannot be marked, prevented by activation, by any other

exception. Cannot be preempted by any other exception

other than Reset.

Asynchronous

3

Hard fault

–1

All classes of fault

Synchronous or

asynchronous

4–10

–

Reserved

–

11

SVCall

Configurable

System service call with SVC instruction

Synchronous

12–13

–

Reserved

–

14

PendSV

Configurable

Pendable request for system service. This is only pended by

software.

Asynchronous

15

SysTick

Configurable

System tick timer has fired.

Asynchronous

16–48

External

interrupt

Configurable

Asserted from outside the processor, IRQ[2n-1:0], and fed

through the NVIC (prioritized).

Asynchronous

相關PDF資料 |

PDF描述 |

|---|---|

| M1A3P1000L-1FG484 | IC FPGA M1 1KB FLASH 1M 484FBGA |

| A3P1000L-1FG484 | IC FPGA 1KB FLASH 1M 484-FBGA |

| AMM24DRMH | CONN EDGECARD 48POS .156 WW |

| A42MX09-1VQG100I | IC FPGA MX SGL CHIP 14K 100VQFP |

| AMM24DRMD | CONN EDGECARD 48POS .156 WW |

相關代理商/技術參數 |

參數描述 |

|---|---|

| M1A3P1000L-1FGG484I | 功能描述:IC FPGA M1 1KB FLASH 1M 484FBGA RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現場可編程門陣列) 系列:ProASIC3L 產品培訓模塊:Three Reasons to Use FPGA's in Industrial Designs Cyclone IV FPGA Family Overview 特色產品:Cyclone? IV FPGAs 標準包裝:60 系列:CYCLONE® IV GX LAB/CLB數:9360 邏輯元件/單元數:149760 RAM 位總計:6635520 輸入/輸出數:270 門數:- 電源電壓:1.16 V ~ 1.24 V 安裝類型:表面貼裝 工作溫度:0°C ~ 85°C 封裝/外殼:484-BGA 供應商設備封裝:484-FBGA(23x23) |

| M1A3P1000L-1PQ208 | 功能描述:IC FPGA M1 1KB FLASH 1M 208PQFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現場可編程門陣列) 系列:ProASIC3L 標準包裝:90 系列:ProASIC3 LAB/CLB數:- 邏輯元件/單元數:- RAM 位總計:36864 輸入/輸出數:157 門數:250000 電源電壓:1.425 V ~ 1.575 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 125°C 封裝/外殼:256-LBGA 供應商設備封裝:256-FPBGA(17x17) |

| M1A3P1000L-1PQ208I | 功能描述:IC FPGA M1 1KB FLASH 1M 208PQFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現場可編程門陣列) 系列:ProASIC3L 標準包裝:40 系列:SX-A LAB/CLB數:6036 邏輯元件/單元數:- RAM 位總計:- 輸入/輸出數:360 門數:108000 電源電壓:2.25 V ~ 5.25 V 安裝類型:表面貼裝 工作溫度:0°C ~ 70°C 封裝/外殼:484-BGA 供應商設備封裝:484-FPBGA(27X27) |

| M1A3P1000L-1PQG208 | 功能描述:IC FPGA M1 1KB FLASH 1M 208PQFP RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現場可編程門陣列) 系列:ProASIC3L 標準包裝:90 系列:ProASIC3 LAB/CLB數:- 邏輯元件/單元數:- RAM 位總計:36864 輸入/輸出數:157 門數:250000 電源電壓:1.425 V ~ 1.575 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 125°C 封裝/外殼:256-LBGA 供應商設備封裝:256-FPBGA(17x17) |

| M1A3P1000L-1PQG208I | 功能描述:IC FPGA M1 1KB FLASH 1M 208PQFP RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現場可編程門陣列) 系列:ProASIC3L 標準包裝:40 系列:SX-A LAB/CLB數:6036 邏輯元件/單元數:- RAM 位總計:- 輸入/輸出數:360 門數:108000 電源電壓:2.25 V ~ 5.25 V 安裝類型:表面貼裝 工作溫度:0°C ~ 70°C 封裝/外殼:484-BGA 供應商設備封裝:484-FPBGA(27X27) |

發(fā)布緊急采購,3分鐘左右您將得到回復。