- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4489 > M1A3P400-1FGG256I (Microsemi SoC)IC FPGA 1KB FLASH 400K 256-FBGA PDF資料下載

參數(shù)資料

| 型號: | M1A3P400-1FGG256I |

| 廠商: | Microsemi SoC |

| 文件頁數(shù): | 11/12頁 |

| 文件大小: | 0K |

| 描述: | IC FPGA 1KB FLASH 400K 256-FBGA |

| 標(biāo)準(zhǔn)包裝: | 90 |

| 系列: | ProASIC3 |

| RAM 位總計: | 55296 |

| 輸入/輸出數(shù): | 178 |

| 門數(shù): | 400000 |

| 電源電壓: | 1.425 V ~ 1.575 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | -40°C ~ 85°C |

| 封裝/外殼: | 256-LBGA |

| 供應(yīng)商設(shè)備封裝: | 256-FPBGA(17x17) |

ARM CortexTM-M1

8P ro d u c t B r i e f

Exception Priority

In the processor exception model, priority determines

when and how the processor takes exceptions. You can

assign software priority levels to interrupts.

The NVIC supports software-assigned priority levels. You

can assign a priority level from 0 to 3 to an interrupt by

writing to the 2-bit IP_N field in an Interrupt Priority

Register. Hardware priority decreases with increasing

interrupt number. Priority level –3 is the highest priority

level, and priority level 3 is the lowest. The priority level

overrides the hardware priority.

Stacks

The processor supports two separate stacks:

Process stack – You can configure Thread mode

to use the process stack. Thread mode uses the

main stack out of reset. SP_process is the Stack

Pointer (SP) register for the process stack.

Main stack – Handler mode uses the main stack.

SP_main is the SP register for the main stack.

Only one stack, the process stack or the main stack, is

visible at any time, using R13. After pushing the content,

the ISR uses the main stack, and all subsequent interrupt

preemptions use the main stack.

Clocking and Resets

The processor has one functional clock input, HCLK, and

one reset signal, SYSRESETn. If debug is implemented,

there is also a SWJ-DP clock, SWCLKTCK, and nTRST.

SWCLKTCK relates to the DAP logic. The debug reset

signal DBGRESETn relates to the debug logic clocked by

HCLK.

The SYSRESETn signal resets the entire processor system

with the exception of debug logic in the following:

Nested Vectored Interrupt Controller (NVIC)

Debug subsystem

The register file cannot be reset by SYSRESETn or

DBGRESETn.

Nested Vectored Interrupt Controller

The NVIC facilitates low-latency exception and interrupt

handling, and implements System Control Registers. The

NVIC supports reprioritizable interrupts. The NVIC and

the processor core interface are closely coupled, which

enables low latency interrupt processing and efficient

processing of late-arriving interrupts. All NVIC registers

are only accessible using word transfers. Any attempt to

write a halfword or byte individually causes corruption

of the register bits. All NVIC registers and system debug

registers are little-endian, regardless of the endianness

state of the processor. See Table 4 for a list of the NVIC

registers and their addresses

.

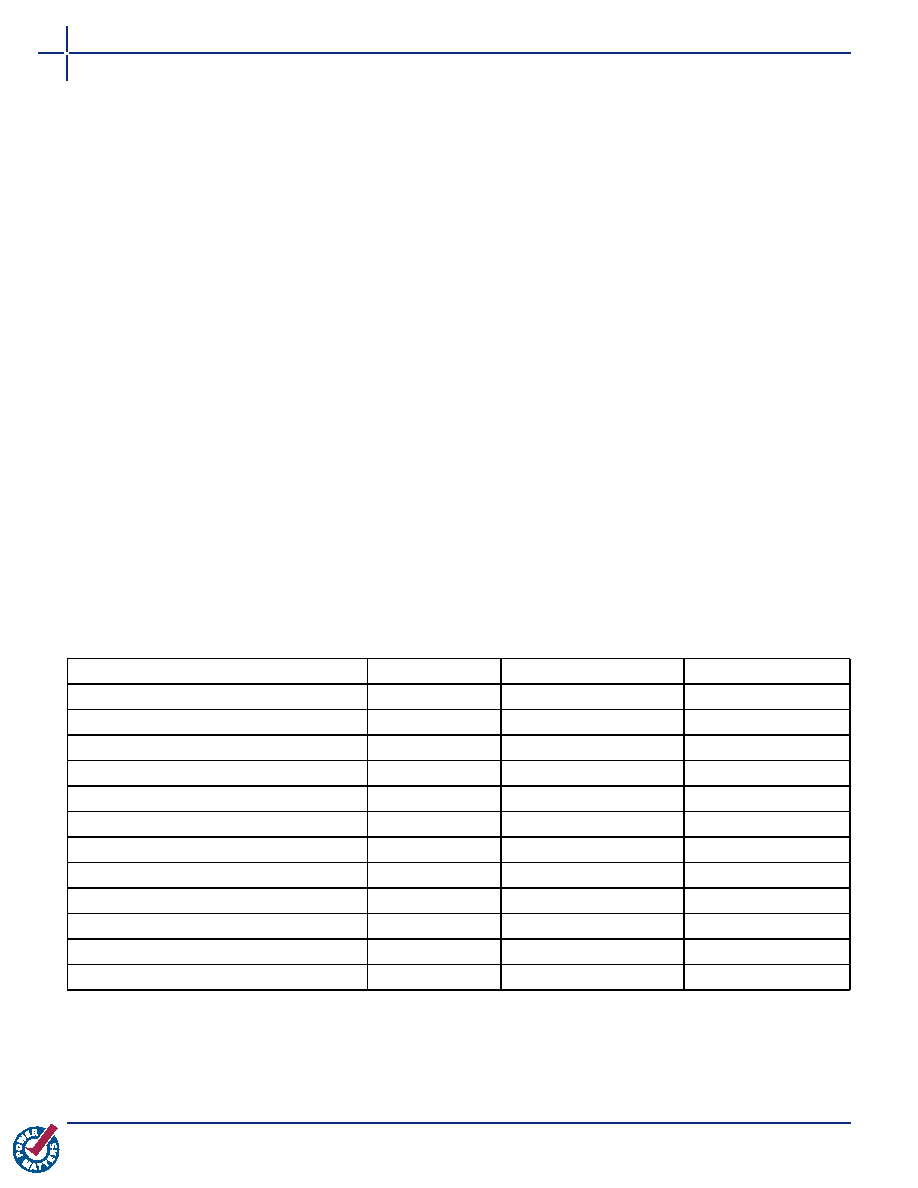

Table 4

NVIC Register

Name of Register

Type

Address

Reset Value

IRQ 0 to 31 Set Enable Register

R/W

0xE000E100

0x00000000

IRQ 0 to 31 Clear Enable Register

R/W

0xE000E180

0x00000000

IRQ 0 to 31 Set Pending Register

R/W

0xE000E200

0x00000000

IRQ 0 to 31 Clear Pending Register

R/W

0xE000E280

0x00000000

Priority 0 Register

R/W

0xE000E400

0x00000000

Priority 1 Register

R/W

0xe000e404

0x00000000

Priority 2 Register

R/W

0xe000e408

0x00000000

Priority 3 Register

R/W

0xe000e40c

0x00000000

Priority 4 Register

R/W

0xe000e410

0x00000000

Priority 5 Register

R/W

0xe000e414

0x00000000

Priority 6 Register

R/W

0xe000e418

0x00000000

Priority 7 Register

R/W

0xe000e41c

0x00000000

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| A3P400-1FGG256I | IC FPGA 1KB FLASH 400K 256-FBGA |

| M1A3P400-1FG256I | IC FPGA 1KB FLASH 400K 256-FBGA |

| A3P400-1FG256I | IC FPGA 1KB FLASH 400K 256-FBGA |

| A54SX08A-FG144A | IC FPGA SX 12K GATES 144-FBGA |

| A54SX08A-FGG144A | IC FPGA SX 12K GATES 144-FBGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M1A3P400-1FGG484 | 功能描述:IC FPGA 1KB FLASH 400K 484-FBGA RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:ProASIC3 標(biāo)準(zhǔn)包裝:90 系列:ProASIC3 LAB/CLB數(shù):- 邏輯元件/單元數(shù):- RAM 位總計:36864 輸入/輸出數(shù):157 門數(shù):250000 電源電壓:1.425 V ~ 1.575 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 125°C 封裝/外殼:256-LBGA 供應(yīng)商設(shè)備封裝:256-FPBGA(17x17) |

| M1A3P400-1FGG484I | 功能描述:IC FPGA 1KB FLASH 400K 484-FBGA RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:ProASIC3 標(biāo)準(zhǔn)包裝:90 系列:ProASIC3 LAB/CLB數(shù):- 邏輯元件/單元數(shù):- RAM 位總計:36864 輸入/輸出數(shù):157 門數(shù):250000 電源電壓:1.425 V ~ 1.575 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 125°C 封裝/外殼:256-LBGA 供應(yīng)商設(shè)備封裝:256-FPBGA(17x17) |

| M1A3P400-1PQ144 | 制造商:ACTEL 制造商全稱:Actel Corporation 功能描述:ProASIC3 Flash Family FPGAs |

| M1A3P400-1PQ144ES | 制造商:ACTEL 制造商全稱:Actel Corporation 功能描述:ProASIC3 Flash Family FPGAs |

| M1A3P400-1PQ144I | 制造商:ACTEL 制造商全稱:Actel Corporation 功能描述:ProASIC3 Flash Family FPGAs |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。