- 您現在的位置:買賣IC網 > PDF目錄180065 > M1A3P600-1FG256 FPGA, 13824 CLBS, 600000 GATES, 350 MHz, PBGA256 PDF資料下載

參數資料

| 型號: | M1A3P600-1FG256 |

| 元件分類: | FPGA |

| 英文描述: | FPGA, 13824 CLBS, 600000 GATES, 350 MHz, PBGA256 |

| 封裝: | 17 X 17 MM, 1.60 MM HEIGHT, 1 MM PITCH, FBGA-256 |

| 文件頁數: | 36/218頁 |

| 文件大小: | 6270K |

| 代理商: | M1A3P600-1FG256 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁當前第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁第173頁第174頁第175頁第176頁第177頁第178頁第179頁第180頁第181頁第182頁第183頁第184頁第185頁第186頁第187頁第188頁第189頁第190頁第191頁第192頁第193頁第194頁第195頁第196頁第197頁第198頁第199頁第200頁第201頁第202頁第203頁第204頁第205頁第206頁第207頁第208頁第209頁第210頁第211頁第212頁第213頁第214頁第215頁第216頁第217頁第218頁

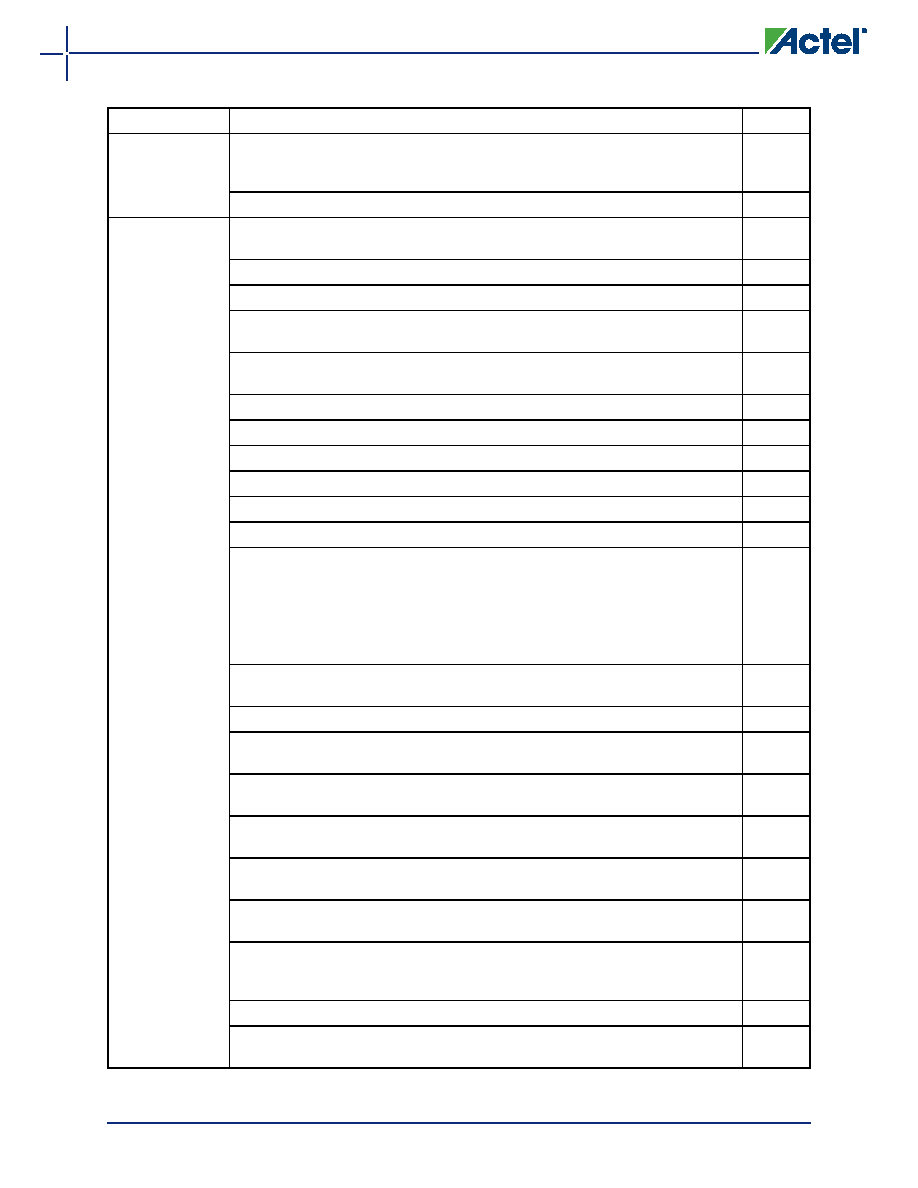

ProASIC3 DC and Switching Characteristics

2- 116

v1.4

Advance v0.7

(continued)

Figure 3-33 Write Access After Write onto Same Address, Figure 3-34 Read

Access After Write onto Same Address, and Figure 3-35 Write Access After

Read onto Same Address are new.

3-82 to

3-84

Figure 3-43 Timing Diagram was updated.

3-96

Advance v0.5

(January 2006)

B-LVDS and M-LDVS are new I/O standards added to the datasheet.

N/A

The term flow-through was changed to pass-through.

N/A

Figure 2-7 Efficient Long-Line Resources was updated.

2-7

The footnotes in Figure 2-15 Clock Input Sources Including CLKBUF,

CLKBUF_LVDS/LVPECL, and CLKINT were updated.

2-16

The Delay Increments in the Programmable Delay Blocks specification in Figure

2-24 ProASIC3E CCC Options.

2-24

The "SRAM and FIFO" section was updated.

2-21

The "RESET" section was updated.

2-25

The "WCLK and RCLK" section was updated.

2-25

The "RESET" section was updated.

2-25

The "RESET" section was updated.

2-27

The "Introduction" of the "Advanced I/Os" section was updated.

2-28

The "I/O Banks" section is new. This section explains the following types of I/Os:

Advanced

Standard+

Standard

Table 2-12 Automotive ProASIC3 Bank Types Definition and Differences is

new. This table describes the standards listed above.

2-29

PCI-X 3.3 V was added to the Compatible Standards for 3.3 V in Table 2-

11 VCCI Voltages and Compatible Standards

2-29

Table 2-13 ProASIC3 I/O Features was updated.

2-30

The "Double Data Rate (DDR) Support" section was updated to include

information concerning implementation of the feature.

2-32

The "Electrostatic Discharge (ESD) Protection" section was updated to include

testing information.

2-35

Level 3 and 4 descriptions were updated in Table 2-43 I/O Hot-Swap and 5 V

Input Tolerance Capabilities in ProASIC3 Devices.

2-64

The notes in Table 2-43 I/O Hot-Swap and 5 V Input Tolerance Capabilities in

ProASIC3 Devices were updated.

2-64

The "Simultaneous Switching Outputs (SSOs) and Printed Circuit Board Layout"

section is new.

2-41

A footnote was added to Table 2-14 Maximum I/O Frequency for Single-Ended

and Differential I/Os in All Banks in Automotive ProASIC3 Devices (maximum

drive strength and high slew selected).

2-30

Table 2-18 Automotive ProASIC3 I/O Attributes vs. I/O Standard Applications

2-45

Table 2-50 ProASIC3 Output Drive (OUT_DRIVE) for Standard I/O Bank Type

(A3P030 device)

2-83

Previous Version

Changes in Current Version (v1.4)

Page

相關PDF資料 |

PDF描述 |

|---|---|

| M1A3P600-1FG484I | FPGA, 13824 CLBS, 600000 GATES, PBGA484 |

| M1A3P600-1FG484 | FPGA, 13824 CLBS, 600000 GATES, 350 MHz, PBGA484 |

| M1A3P600-1FGG144I | FPGA, 13824 CLBS, 600000 GATES, PBGA144 |

| M1A3P600-1FGG144 | FPGA, 13824 CLBS, 600000 GATES, 350 MHz, PBGA144 |

| M1A3P600-1FGG256I | FPGA, 13824 CLBS, 600000 GATES, PBGA256 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| M1A3P600-1FG256I | 功能描述:IC FPGA 1KB FLASH 600K 256-FBGA RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現場可編程門陣列) 系列:ProASIC3 標準包裝:90 系列:ProASIC3 LAB/CLB數:- 邏輯元件/單元數:- RAM 位總計:36864 輸入/輸出數:157 門數:250000 電源電壓:1.425 V ~ 1.575 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 125°C 封裝/外殼:256-LBGA 供應商設備封裝:256-FPBGA(17x17) |

| M1A3P600-1FG484 | 功能描述:IC FPGA 1KB FLASH 600K 484-FBGA RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現場可編程門陣列) 系列:ProASIC3 標準包裝:90 系列:ProASIC3 LAB/CLB數:- 邏輯元件/單元數:- RAM 位總計:36864 輸入/輸出數:157 門數:250000 電源電壓:1.425 V ~ 1.575 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 125°C 封裝/外殼:256-LBGA 供應商設備封裝:256-FPBGA(17x17) |

| M1A3P600-1FG484I | 功能描述:IC FPGA 1KB FLASH 600K 484-FBGA RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現場可編程門陣列) 系列:ProASIC3 標準包裝:40 系列:SX-A LAB/CLB數:6036 邏輯元件/單元數:- RAM 位總計:- 輸入/輸出數:360 門數:108000 電源電壓:2.25 V ~ 5.25 V 安裝類型:表面貼裝 工作溫度:0°C ~ 70°C 封裝/外殼:484-BGA 供應商設備封裝:484-FPBGA(27X27) |

| M1A3P600-1FGG144 | 功能描述:IC FPGA 1KB FLASH 600K 144-FBGA RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現場可編程門陣列) 系列:ProASIC3 標準包裝:90 系列:ProASIC3 LAB/CLB數:- 邏輯元件/單元數:- RAM 位總計:36864 輸入/輸出數:157 門數:250000 電源電壓:1.425 V ~ 1.575 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 125°C 封裝/外殼:256-LBGA 供應商設備封裝:256-FPBGA(17x17) |

| M1A3P600-1FGG144ES | 制造商:ACTEL 制造商全稱:Actel Corporation 功能描述:ProASIC3 Flash Family FPGAs |

發(fā)布緊急采購,3分鐘左右您將得到回復。