- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄358972 > M24C64-WMN6 (意法半導(dǎo)體) The CAT24FC02 is a 2-kb Serial CMOS EEPROM internally organized as 256 words of 8 bits each PDF資料下載

參數(shù)資料

| 型號: | M24C64-WMN6 |

| 廠商: | 意法半導(dǎo)體 |

| 元件分類: | EEPROM |

| 英文描述: | The CAT24FC02 is a 2-kb Serial CMOS EEPROM internally organized as 256 words of 8 bits each |

| 中文描述: | 該CAT24FC02是一個2 KB的EEPROM的國內(nèi)256個8位每字舉辦的串行CMOS |

| 文件頁數(shù): | 9/26頁 |

| 文件大?。?/td> | 394K |

| 代理商: | M24C64-WMN6 |

9/26

M24C64, M24C32

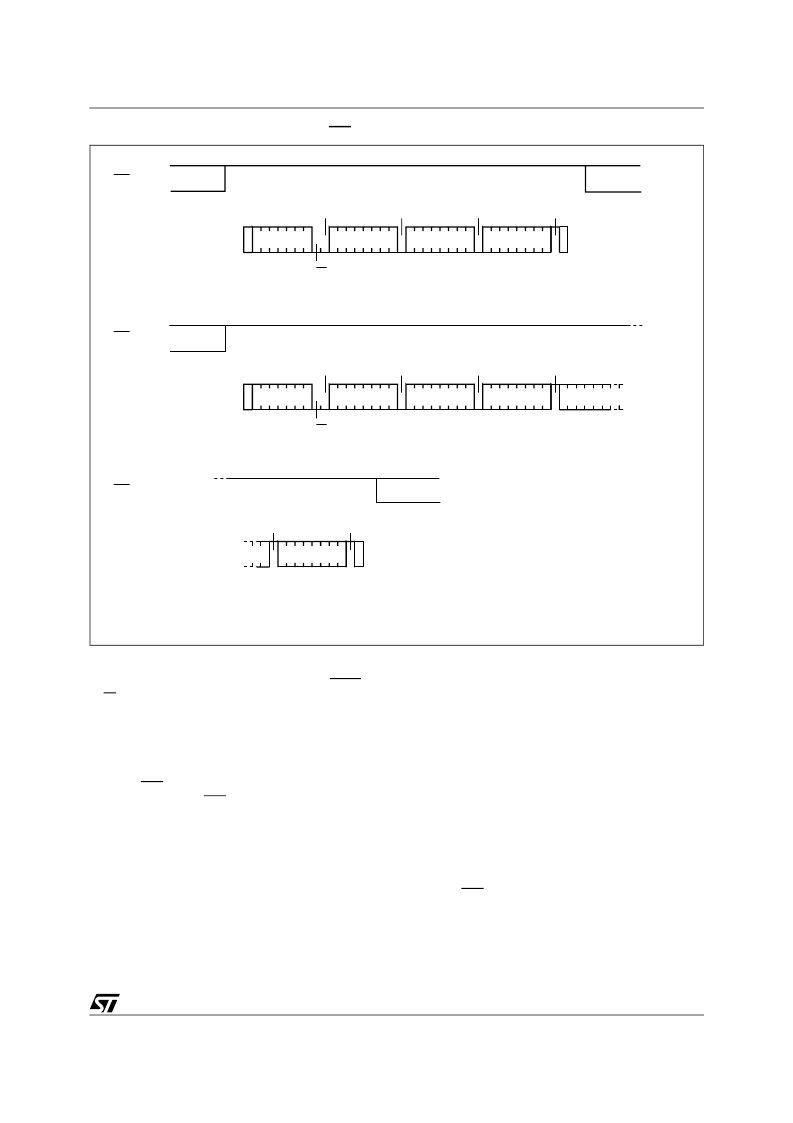

Figure 7. Write Mode Sequences with WC=1 (data write inhibited)

Write Operations

Following a Start condition the bus master sends

a Device Select Code with the Read/Write bit

(RW) reset to 0. The device acknowledges this, as

shown in

Figure 8.

, and waits for two address

bytes. The device responds to each address byte

with an acknowledge bit, and then waits for the

data byte.

Writing to the memory may be inhibited if Write

Control (WC) is driven High. Any Write instruction

with Write Control (WC) driven High (during a pe-

riod of time from the Start condition until the end of

the two address bytes) will not modify the memory

contents, and the accompanying data bytes are

notacknowledged, as shown in

Figure 7.

.

Each data byte in the memory has a 16-bit (two

byte wide) address. The Most Significant Byte (

Ta-

ble 4.

) is sent first, followed by the Least Signifi-

cant Byte (

Table 5.

). Bits b15 to b0 form the

address of the byte in memory.

When the bus master generates a Stop condition

immediately after the Ack bit (in the “10

th

bit” time

slot), either at the end of a Byte Write or a Page

Write, the internal Write cycle is triggered. A Stop

condition at any other time slot does not trigger the

internal Write cycle.

After the Stop condition, the delay t

W

, and the suc-

cessful completion of a Write operation, the de-

vice’s internal address counter is incremented

automatically, to point to the next byte address af-

ter the last one that was modified.

During the internal Write cycle, Serial Data (SDA)

is disabled internally, and the device does not re-

spond to any requests.

Byte Write

After the Device Select code and the address

bytes, the bus master sends one data byte. If the

addressed location is Write-protected, by Write

Control (WC) being driven High, the device replies

with NoAck, and the location is not modified. If, in-

stead, the addressed location is not Write-protect-

ed, the device replies with Ack. The bus master

terminates the transfer by generating a Stop con-

dition, as shown in

Figure 8.

.

S

S

BYTE WRITE

DEV SEL

BYTE ADDR

BYTE ADDR

DATA IN

WC

S

PAGE WRITE

DEV SEL

BYTE ADDR

BYTE ADDR

DATA IN 1

WC

DATA IN 2

AI01120C

PAGE WRITE

(cont'd)

WC (cont'd)

S

DATA IN N

ACK

ACK

ACK

NO ACK

R/W

ACK

ACK

ACK

NO ACK

R/W

NO ACK

NO ACK

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M24C64-WMN6P | The CAT24FC02 is a 2-kb Serial CMOS EEPROM internally organized as 256 words of 8 bits each |

| M24C64-WMN6T | 18-Bit Universal Bus Transceiver With 3-State Outputs 56-SSOP -40 to 85 |

| M24C64-MB3TP | 16-Bit Transparent D-Type Latch With 3-State Outputs 54-BGA MICROSTAR JUNIOR -40 to 85 |

| M24C64-MB6 | 16-Bit Transparent D-Type Latch With 3-State Outputs 48-TSSOP -40 to 85 |

| M24C64-MB6P | 16-Bit Transparent D-Type Latch With 3-State Outputs 56-BGA MICROSTAR JUNIOR -40 to 85 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M24C64-WMN6P | 功能描述:電可擦除可編程只讀存儲器 2.5-5.5V 64K (8Kx8) RoHS:否 制造商:Atmel 存儲容量:2 Kbit 組織:256 B x 8 數(shù)據(jù)保留:100 yr 最大時鐘頻率:1000 KHz 最大工作電流:6 uA 工作電源電壓:1.7 V to 5.5 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:SOIC-8 |

| M24C64-WMN6T | 功能描述:電可擦除可編程只讀存儲器 5.5V 64K (8Kx8) RoHS:否 制造商:Atmel 存儲容量:2 Kbit 組織:256 B x 8 數(shù)據(jù)保留:100 yr 最大時鐘頻率:1000 KHz 最大工作電流:6 uA 工作電源電壓:1.7 V to 5.5 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:SOIC-8 |

| M24C64WMN6TP | 制造商:ST MICRO 功能描述:Pb Free |

| M24C64-WMN6TP | 功能描述:電可擦除可編程只讀存儲器 電可擦除可編程只讀存儲器 S. I2C 64k RoHS:否 制造商:Atmel 存儲容量:2 Kbit 組織:256 B x 8 數(shù)據(jù)保留:100 yr 最大時鐘頻率:1000 KHz 最大工作電流:6 uA 工作電源電壓:1.7 V to 5.5 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:SOIC-8 |

| M24C64-WMN6TP/P | 制造商:STMicroelectronics 功能描述:EEPROM SERL-I2C 64KBIT 8KX8 3.3V/5V 8PIN SO N - Tape and Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。