- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄67762 > M37150MA-XXXFP 8-BIT, MROM, 8.95 MHz, MICROCONTROLLER, PDSO42 PDF資料下載

參數(shù)資料

| 型號(hào): | M37150MA-XXXFP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-BIT, MROM, 8.95 MHz, MICROCONTROLLER, PDSO42 |

| 封裝: | 0.450 INCH, 0.80 MM PITCH, PLASTIC, SSOP-42 |

| 文件頁(yè)數(shù): | 55/80頁(yè) |

| 文件大小: | 1092K |

| 代理商: | M37150MA-XXXFP |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)當(dāng)前第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)

M37150M6/M8/MA/MC/MF-XXXFP, M37150EFFP

Rev.1.00

Nov 01, 2002

page 57 of 139

REJ03B0128-0100Z

8.10.7 Reference Voltage Generating Circuit

and Comparator

The composite video signal clamped by the clamping circuit is input

to the reference voltage generating circuit and the comparator.

(1) Reference voltage generating circuit

This circuit generates a reference voltage (slice voltage) by us-

ing the amplitude of the clock run-in pulse in the line specified by

the data slice line specification circuit. Connect a capacitor be-

tween the VHOLD pin and the VSS pin, and make the length of

wiring as short as possible to prevent a leakage current from be-

ing generated.

(2) Comparator

The comparator compares the voltage of the composite video

signal with the voltage (reference voltage) generated in the refer-

ence voltage generating circuit, and converts the composite video

signal into a digital value.

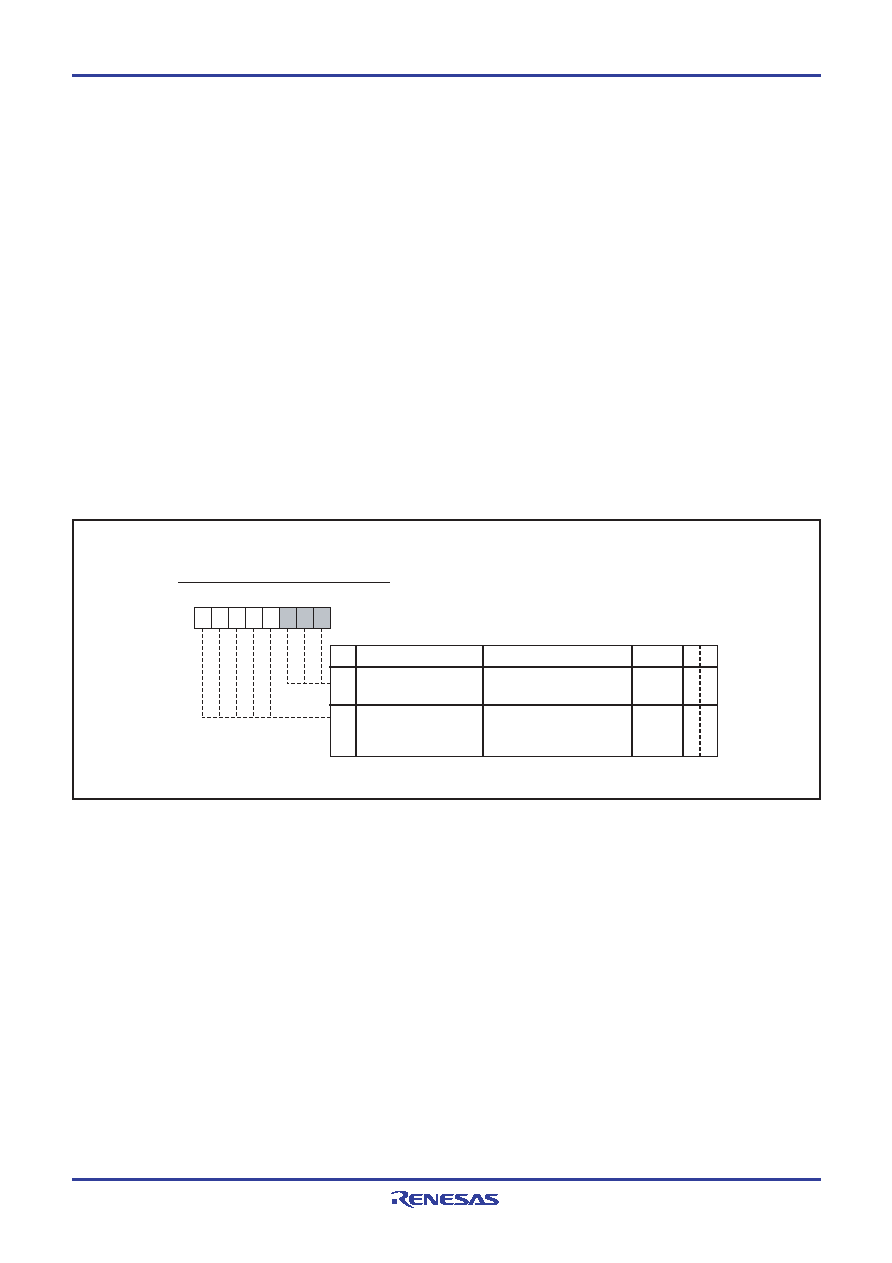

Fig. 8.10.10 Clock Run-in Detect Register

8.10.8 Start Bit Detecting Circuit

This circuit detects a start bit at the line decided in the data slice line

specification circuit.

The detection of a start bit is as follows:.

A sampling clock is generated by dividing the reference clock out-

put by the timing signal.

A clock run-in pulse is detected by the sampling clock.

After detection of the pulse, a start bit pattern is detected from the

comparator output.

8.10.9 Clock Run-in Determination Circuit

This circuit determinates clock run-in by counting the number of pulses

in a window of the composite video signal.

The reference clock count value in one pulse cycle is stored in bits 3

to 7 of the clock run-in detect register (address 00E416). Read out

these bits after the occurrence of a data slicer interrupt (refer to

“8.10.12 Interrupt Request Generating Circuit”).

Figure 8.10.10 shows the structure of the clock run-in detect register.

b7 b6 b5 b4 b3 b2 b1 b0

Clock run-in detect register (CRD) [Address 00E416]

R W

Clock Run-in Detect Register

0

to

2

0

R—

Test bits

3

to

7

Number of reference clocks to

be counted in one clock run-in

pulse period.

Clock run-in detection

bit(CRD3 to CRD7)

0

R—

Read-only

After reset

Functions

Nam

Be

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M37151M8-XXXFP | 8-BIT, MROM, 8.1 MHz, MICROCONTROLLER, PDSO42 |

| M37151MF-XXXFP | 8-BIT, MROM, 8.1 MHz, MICROCONTROLLER, PDSO42 |

| M37151MA-XXXFP | 8-BIT, MROM, 8.1 MHz, MICROCONTROLLER, PDSO42 |

| M37161M8-XXXFP | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDSO42 |

| M37161EFSP | 8-BIT, OTPROM, 8 MHz, MICROCONTROLLER, PDIP42 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M37150MC | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SNGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M37150MC-XXXFP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SNGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M37150MF | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SNGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M37150MF-XXXFP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SNGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M37151 | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER with CLOSED CAPTION DECODER and ON-SCREEN DISPLAY CONTROLLER |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。