Rev.4.01

Nov 14, 2003

page 57 of 136

3803/3804 Group

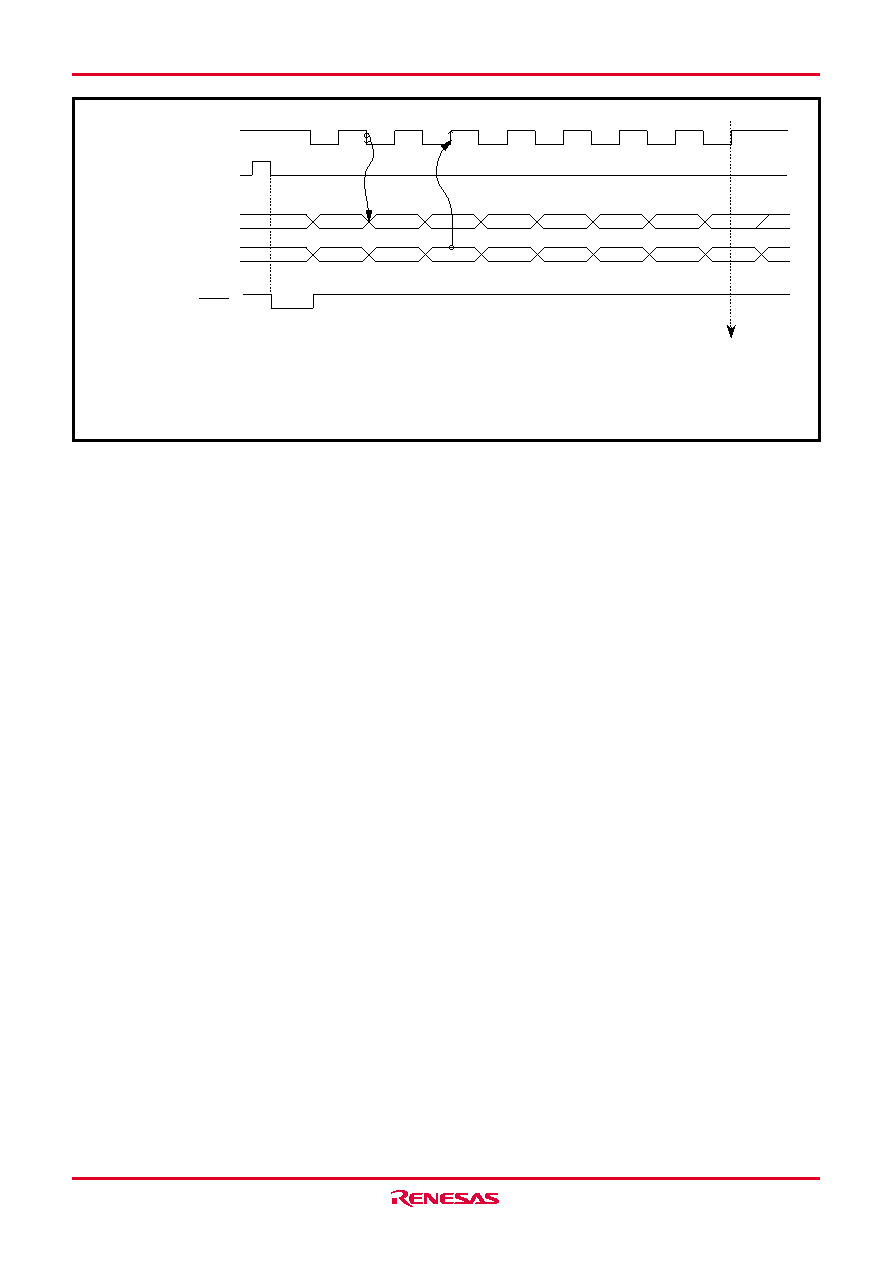

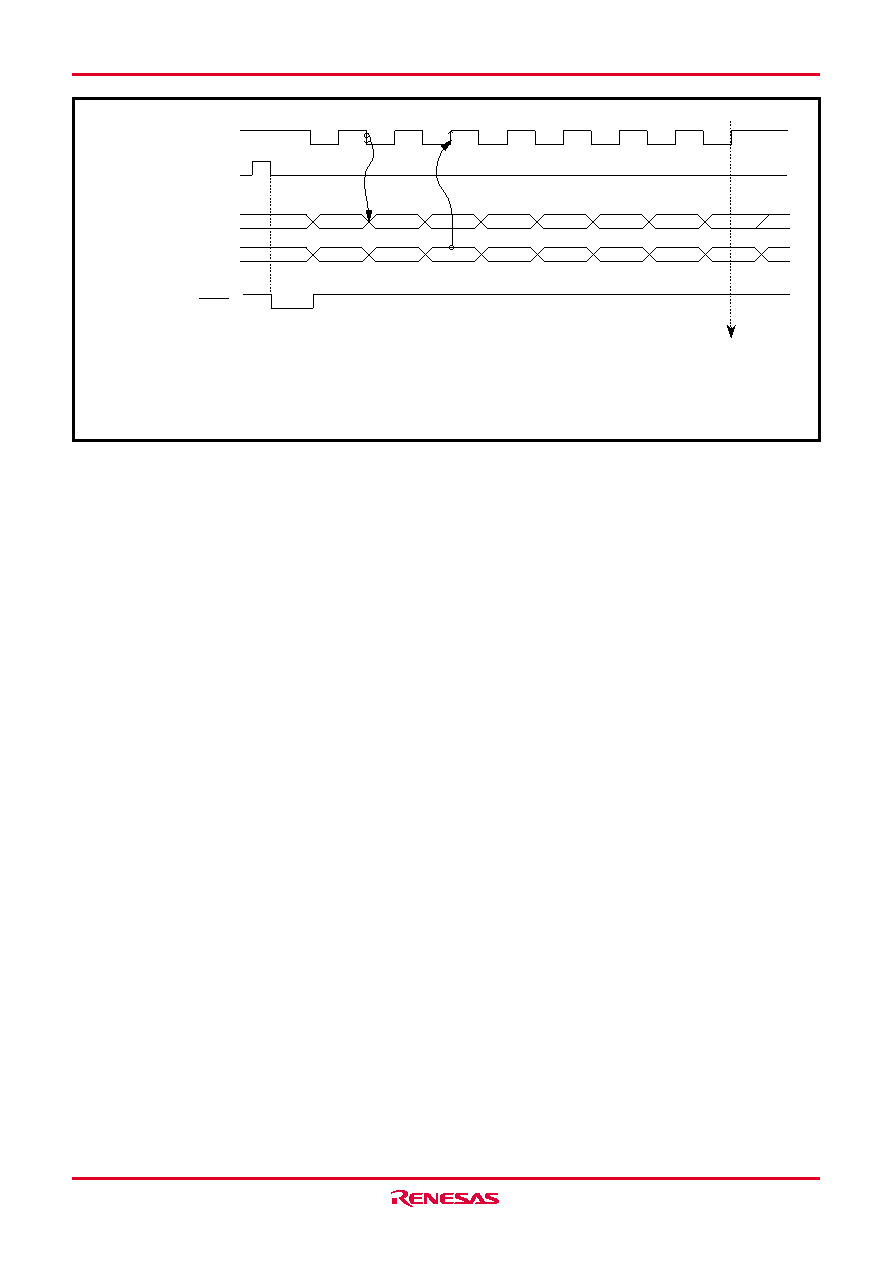

Fig. 47 Timing of serial I/O2

D7

D0

D1

D2

D3

D4

D5

D6

Transfer clock (Note 1)

Serial I/O2 output SOUT2

Serial I/O2 input SIN2

Receive enable signal SRDY2

Serial I/O2 register

write signal

(Note 2)

Serial I/O2 interrupt request bit set

1: When the internal clock is selected as the transfer clock, the divide ratio of f(XIN), or f(XCIN) in low-speed mode, can be

selected by setting bits 0 to 2 of the serial I/O2 control register.

2: When the internal clock is selected as the transfer clock, the SOUT2 pin goes to high impedance after transfer completion.

Notes