- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄370946 > M38276E6-XXXHP (Mitsubishi Electric Corporation) SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER PDF資料下載

參數(shù)資料

| 型號(hào): | M38276E6-XXXHP |

| 廠商: | Mitsubishi Electric Corporation |

| 英文描述: | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| 中文描述: | 單芯片8位CMOS微機(jī) |

| 文件頁(yè)數(shù): | 19/70頁(yè) |

| 文件大小: | 1112K |

| 代理商: | M38276E6-XXXHP |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)當(dāng)前第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)

19

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

MITSUBISHI MICROCOMPUTERS

3827 Group

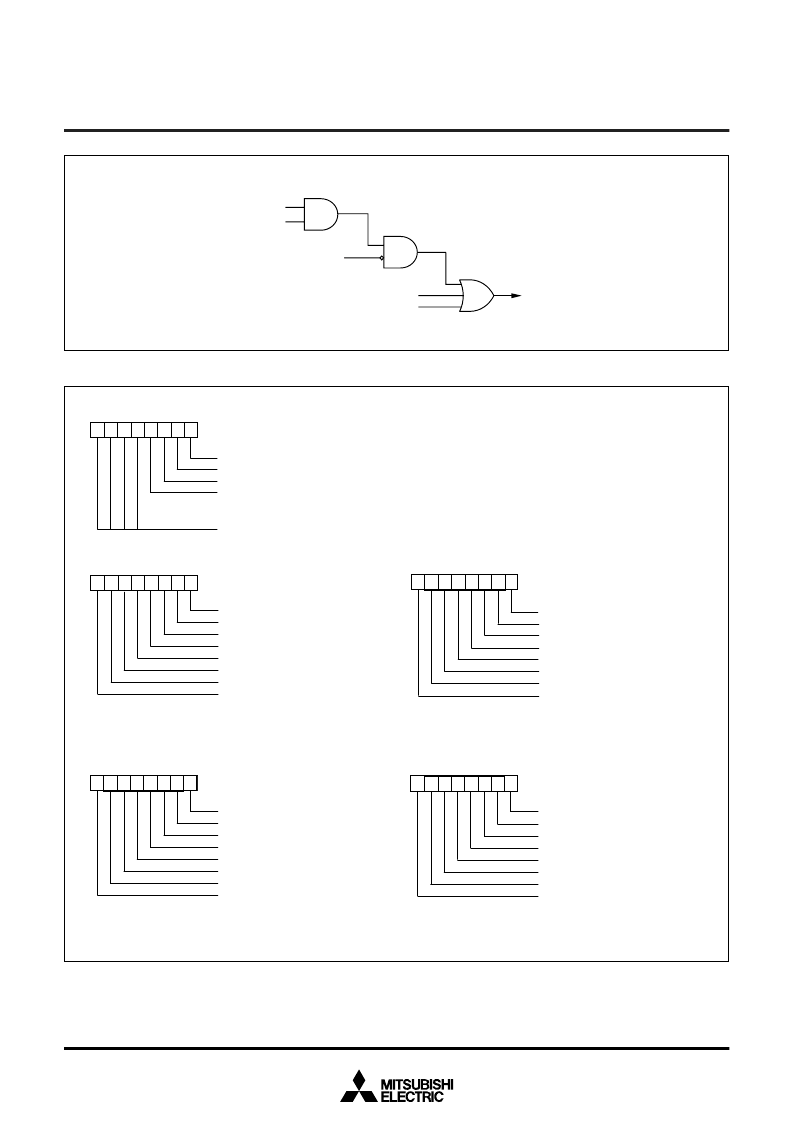

Fig. 14 Interrupt control

Fig. 15 Structure of interrupt-related registers

b7

b0

Interrupt edge selection register

(INTEDGE : address 003A

16

)

INT

0

interrupt edge selection bit

INT

1

interrupt edge selection bit

INT

2

interrupt edge selection bit

INT

3

interrupt edge selection bit

Not used (return “0” when read)

Interrupt request register 1

(IREQ1 : address 003C

16

)

INT

0

interrupt request bit

INT

1

interrupt request bit

Serial I/O1 receive interrupt request bit

Serial I/O1 transmit interrupt request bit

Timer X interrupt request bit

Timer Y interrupt request bit

Timer 2 interrupt request bit

Timer 3 interrupt request bit

Interrupt control register 1

(ICON1 : address 003E

16

)

INT

0

interrupt enable bit

INT

1

interrupt enable bit

Serial I/O receive interrupt enable bit

Serial I/O transmit interrupt enable bit

Timer X interrupt enable bit

Timer Y interrupt enable bit

Timer 2 interrupt enable bit

Timer 3 interrupt enable bit

0 : No interrupt request issued

1 : Interrupt request issued

Interrupt request register 2

(IREQ2 : address 003D

16

)

CNTR

0

interrupt request bit

CNTR

1

interrupt request bit

Timer 1 interrupt request bit

INT

2

interrupt request bit

Serial I/O2 interrupt request bit

Key input interrupt request bit

ADT/AD conversion interrupt request bit

Not used (returns “0” when read)

Interrupt control register 2

(ICON2 : address 003F

16

)

CNTR

0

interrupt enable bit

CNTR

1

interrupt enable bit

Timer 1 interrupt enable bit

INT

2

interrupt enable bit

Serial I/O2 interrupt enable bit

Key input interrupt enable bit

ADT/AD conversion interrupt enable bit

Not used (returns “0” when read)

(Do not write “1” to this bit.)

0 : Interrupts disabled

1 : Interrupts enabled

0 : Falling edge active

1 : Rising edge active

b7

b0

b7

b0

b7

b0

b7

b0

Interrupt request bit

Interrupt enable bit

Interrupt disable flag (I)

BRK instruction

Reset

Interrupt request

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M38276E8-XXXFP | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M38276E8-XXXFS | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M38276E8-XXXGP | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M38276E8-XXXHP | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M38276E9-XXXFP | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M3828 BK001 | 制造商:Alpha Wire Company 功能描述:CBL 3COND 16AWG BLK 1000' |

| M3828 BK002 | 制造商:Alpha Wire Company 功能描述:CBL 3COND 16AWG BLK 500' |

| M3828 BK005 | 制造商:Alpha Wire Company 功能描述:CBL 3COND 16AWG BLK 100' |

| M3828 BK199 | 制造商:Alpha Wire Company 功能描述:CBL 3COND 16AWG BLK 3000=3000' |

| M3829 BK001 | 制造商:Alpha Wire Company 功能描述:CBL 4COND 16AWG BLK 1000' |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。