- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370911 > M38276E7-XXXFS (Mitsubishi Electric Corporation) SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER PDF資料下載

參數(shù)資料

| 型號: | M38276E7-XXXFS |

| 廠商: | Mitsubishi Electric Corporation |

| 英文描述: | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| 中文描述: | 單芯片8位CMOS微機 |

| 文件頁數(shù): | 11/70頁 |

| 文件大小: | 1112K |

| 代理商: | M38276E7-XXXFS |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁當(dāng)前第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁

11

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

MITSUBISHI MICROCOMPUTERS

3827 Group

I/O PORTS

Direction Registers

The I/O ports have direction registers which determine the input/

output direction of each individual pin. (P0

0

–P0

7

and P1

0

–P1

5

use

bit 0 of port P0, P1 direction registers respectively.)

When “1” is written to that bit, that pin becomes an output pin.

When “0” is written to the bit corresponding to a pin, that pin be-

comes an input pin.

If data is read from a pin set to output, the value of the port output

latch is read, not the value of the pin itself. Pins set to input are

floating and the value of that pin can be read. If a pin set to input

is written to, only the port output latch is written to and the pin re-

mains floating.

Port P3 Output Control Register

Bit 0 of the port P3 output control register (address 0007

16

) en-

ables control of the output of ports P3

0

to P3

7

.

When the bit is set to “1”, the port output function is valid.

When resetting, bit 0 of the port P3 output control register is set to

“0” (the port output function is invalid.) and ports P3

0

to P3

7

are

pulled up.

Pull-up Control

By setting the PULL register A (address 0016

16

) or the PULL reg-

ister B (address 0017

16

), ports P0 to P6 can control pull-up with a

program.

However, the contents of PULL register A and PULL register B do

not affect ports programmed as the output ports.

The PULL register A setting is invalid for pins set to segment out-

put on the segment output enable register.

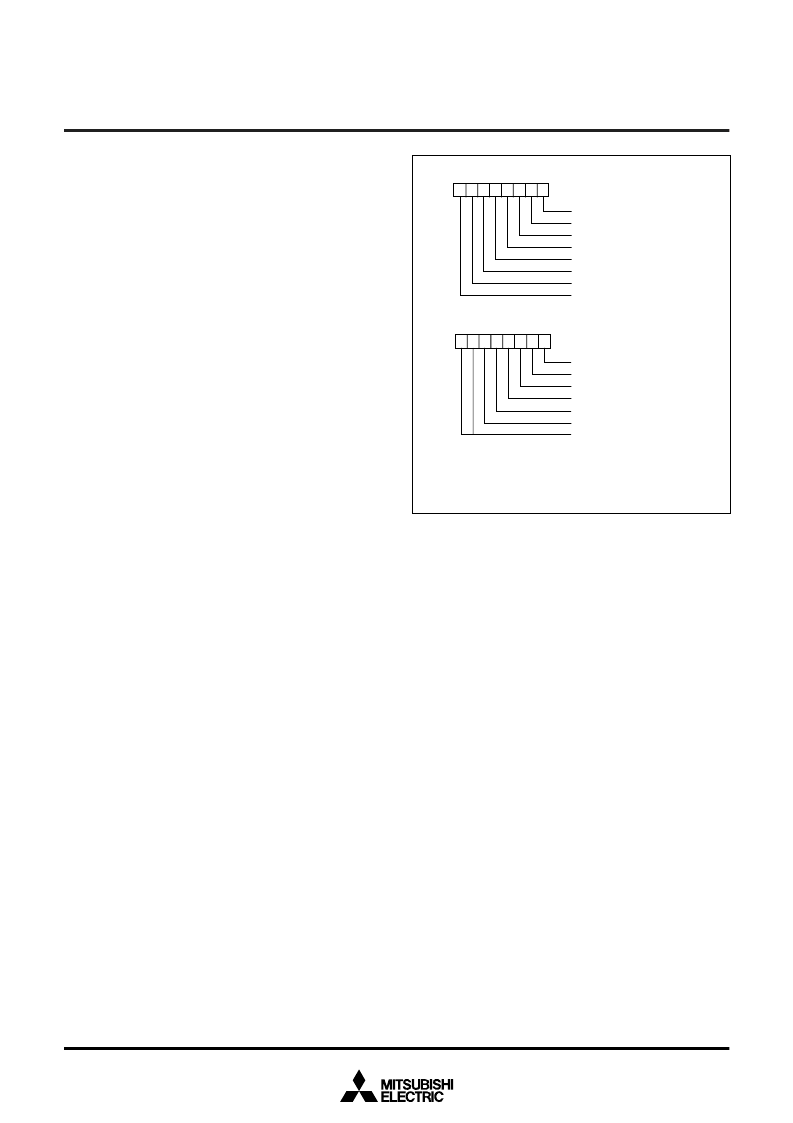

Fig. 9 Structure of PULL register A and PULL register B

P0

0

,

P

0

1

pull-up

P0

2

,

P0

3

pull-up

P0

4

–P0

7

pull-up

P1

0

–P1

3

pull-up

P1

4

,

P1

5

pull-up

P1

6

,

P1

7

pull-up

P2

0

–P2

3

pull-up

P2

4

–P2

7

pull-up

PULL register A

(PULLA : address 0016

16

b7

b0

P4

1

–P4

3

pull-up

P4

4

–P4

7

pull-up

P5

0

–P5

3

pull-up

P5

4

–P5

7

pull-up

P6

0

–P6

3

pull-up

P6

4

–P6

7

pull-up

Not used (return “0” when read)

0 : No pull-up

1 : Pull-up

PULL register B

(PULLB : address 0017

16

)

b7

b0

Note :

The contents of PULL register A and PULL register B

do not affect ports programmed as the output port.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M38276E7-XXXGP | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M38276E7-XXXHP | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M38276EB-XXXFP | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M38276EB-XXXFS | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M38276EB-XXXGP | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M3828 BK001 | 制造商:Alpha Wire Company 功能描述:CBL 3COND 16AWG BLK 1000' |

| M3828 BK002 | 制造商:Alpha Wire Company 功能描述:CBL 3COND 16AWG BLK 500' |

| M3828 BK005 | 制造商:Alpha Wire Company 功能描述:CBL 3COND 16AWG BLK 100' |

| M3828 BK199 | 制造商:Alpha Wire Company 功能描述:CBL 3COND 16AWG BLK 3000=3000' |

| M3829 BK001 | 制造商:Alpha Wire Company 功能描述:CBL 4COND 16AWG BLK 1000' |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。