- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370954 > M388504E6SP (Mitsubishi Electric Corporation) SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER PDF資料下載

參數(shù)資料

| 型號: | M388504E6SP |

| 廠商: | Mitsubishi Electric Corporation |

| 英文描述: | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| 中文描述: | 單芯片8位CMOS微機(jī) |

| 文件頁數(shù): | 7/51頁 |

| 文件大小: | 736K |

| 代理商: | M388504E6SP |

第1頁第2頁第3頁第4頁第5頁第6頁當(dāng)前第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁

7

3850 Group (Spec. H)

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

MITSUBISHI MICROCOMPUTERS

FUNCTIONAL DESCRIPTION

CENTRAL PROCESSING UNIT (CPU)

The 3850 group (spec. H) uses the standard 740 Family instruc-

tion set. Refer to the table of 740 Family addressing modes and

machine instructions or the 740 Family Software Manual for de-

tails on the instruction set.

Machine-resident 740 Family instructions are as follows:

The FST and SLW instructions cannot be used.

The STP, WIT, MUL, and DIV instructions can be used.

[Accumulator (A)]

The accumulator is an 8-bit register. Data operations such as data

transfer, etc., are executed mainly through the accumulator.

[Index Register X (X)]

The index register X is an 8-bit register. In the index addressing

modes, the value of the OPERAND is added to the contents of

register X and specifies the real address.

[Index Register Y (Y)]

The index register Y is an 8-bit register. In partial instruction, the

value of the OPERAND is added to the contents of register Y and

specifies the real address.

[Stack Pointer (S)]

The stack pointer is an 8-bit register used during subroutine calls

and interrupts. This register indicates start address of stored area

(stack) for storing registers during subroutine calls and interrupts.

The low-order 8 bits of the stack address are determined by the

contents of the stack pointer. The high-order 8 bits of the stack ad-

dress are determined by the stack page selection bit. If the stack

page selection bit is “0” , the high-order 8 bits becomes “00

16

”. If

the stack page selection bit is “1”, the high-order 8 bits becomes

“01

16

”.

The operations of pushing register contents onto the stack and

popping them from the stack are shown in Figure 6.

Store registers other than those described in Figure 6 with pro-

gram when the user needs them during interrupts or subroutine

calls.

[Program Counter (PC)]

The program counter is a 16-bit counter consisting of two 8-bit

registers PC

H

and PC

L

. It is used to indicate the address of the

next instruction to be executed.

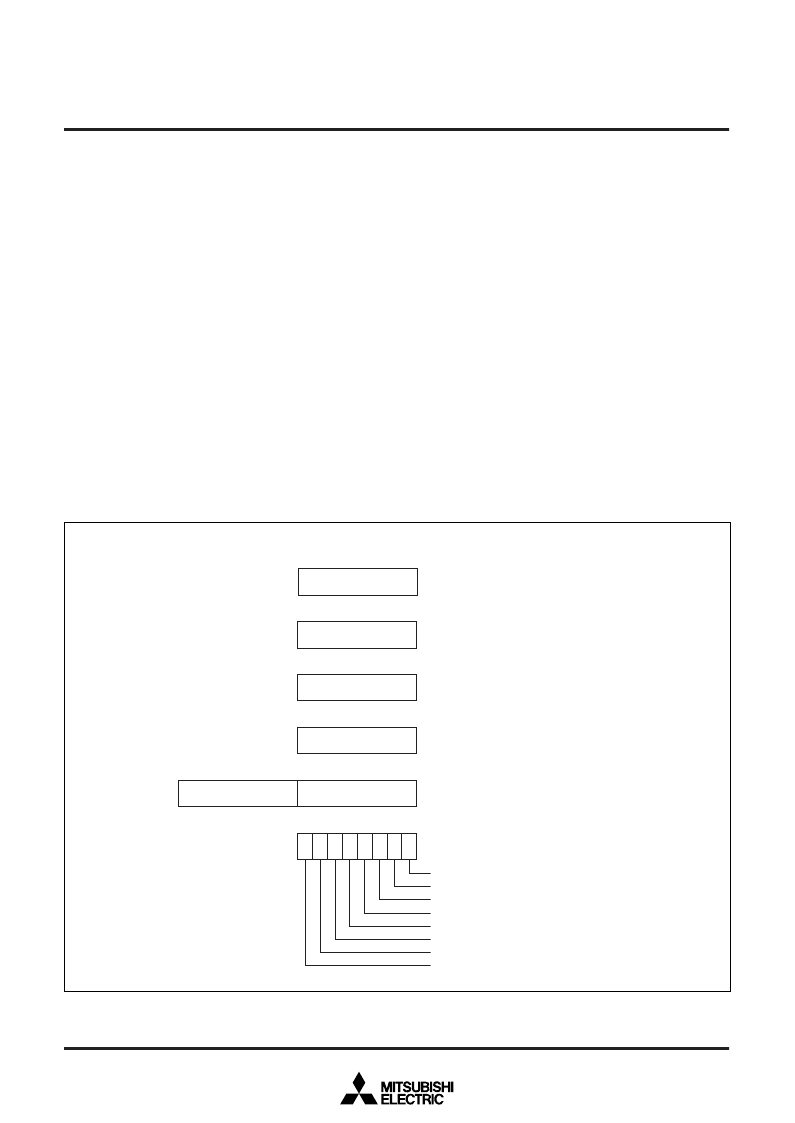

Fig. 5 740 Family CPU register structure

A

Accumulator

b7

b7

b7

b7

b0

b7

b15

b0

b7

b0

b0

b0

b0

X

Index register X

Y

Index register Y

S

Stack pointer

PC

L

Program counter

PC

H

N V T B D I Z C

Processor status register (PS)

Carry flag

Zero flag

Interrupt disable flag

Decimal mode flag

Break flag

Index X mode flag

Overflow flag

Negative flag

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M388504E6SS | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M3850 | Single Chip 8 Bits Microcomputer(8位單片機(jī)) |

| M388504E6FP | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M38867E8A-XXXHP | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M38867E8AHP | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M388504E6SS | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M38850F1-HP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M38850F2-HP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M38850F3-HP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M38850F4-HP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。