- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄180205 > M393B5273CH0-CK0 512M X 72 MULTI DEVICE DRAM MODULE, 0.225 ns, DMA240 PDF資料下載

參數(shù)資料

| 型號: | M393B5273CH0-CK0 |

| 元件分類: | DRAM |

| 英文描述: | 512M X 72 MULTI DEVICE DRAM MODULE, 0.225 ns, DMA240 |

| 封裝: | HALOGEN FREE AND ROHS COMPLIANT, DIMM-240 |

| 文件頁數(shù): | 8/58頁 |

| 文件大小: | 1982K |

| 代理商: | M393B5273CH0-CK0 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁當(dāng)前第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁

datasheet

DDR3 SDRAM

Rev. 1.0

Registered DIMM

- 16 -

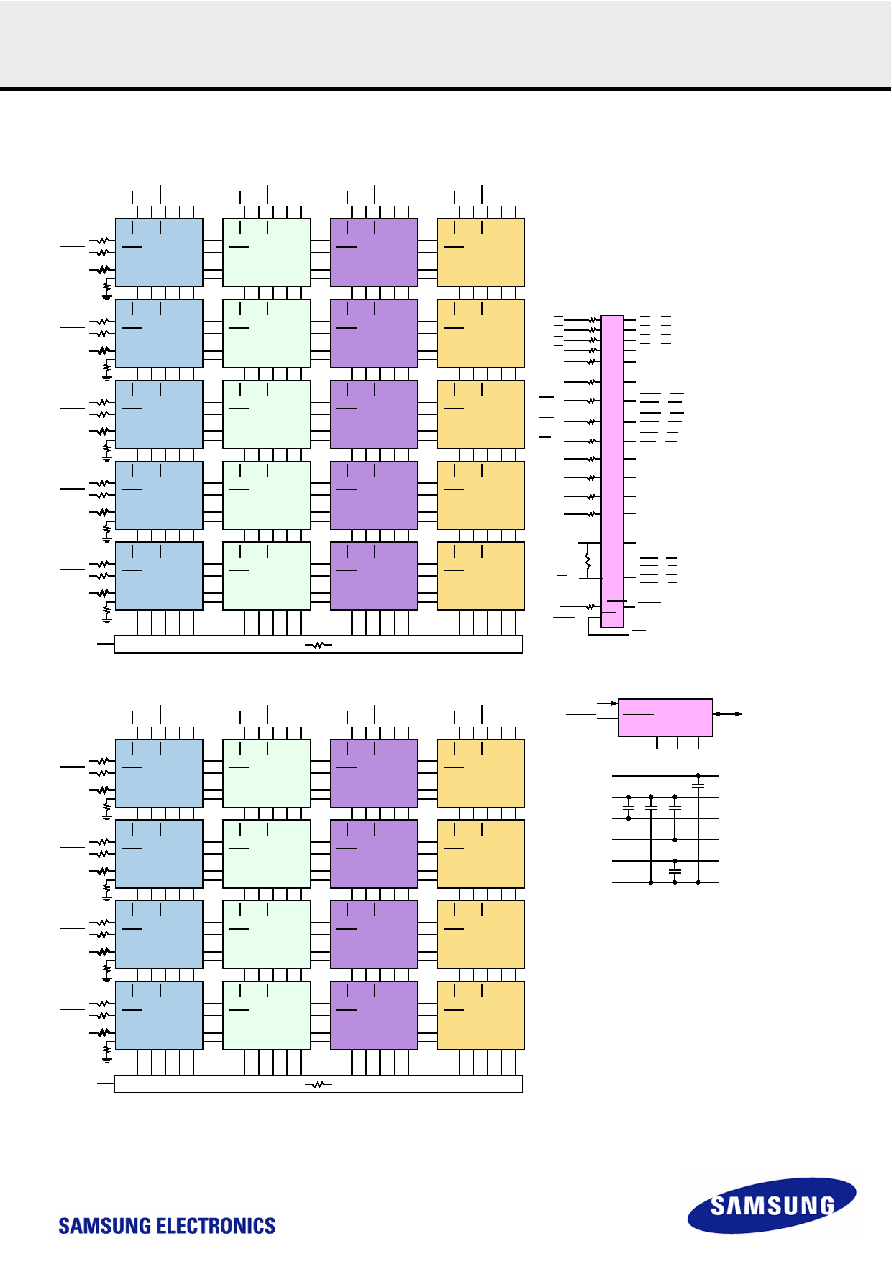

10.5 8GB, 1Gx72 Module (Populated as 4 ranks of x8 DDR3 SDRAMs)

DQS0

DQ[7:0]

DQS

DQ[7:0]

U0

CK

CS

CK

E

ODT

ZQ

PCK

0

CS

0

PCK

0

WCK

E

0

WO

DT0

DQS

DQ[7:0]

U9

CK

CS

CK

E

ODT

ZQ

PCK

0

CS

1

PCK

0

WCK

E

1

VDD

DQS

DQ[7:0]

U18

CK

CS

CK

E

ODT

ZQ

PCK

2

CS

2

PCK

2

WCK

E

0

WO

DT1

DQS

DQ[7:0]

U27

CK

CS

CK

E

ODT

ZQ

PCK

2

CS

3

PCK

2

WCK

E

1

VDD

DQS1

DQ[15:8]

DQS

DQ[7:0]

U1

CK

CS

CK

E

OD

T

ZQ

DQS

DQ[7:0]

U10

CK

CS

CK

E

OD

T

ZQ

DQS

DQ[7:0]

U19

CK

CS

CK

E

OD

T

ZQ

DQS

DQ[7:0]

U28

CK

CS

CK

E

OD

T

ZQ

DQS2

DQ[23:16]

DQS

DQ[7:0]

U2

CK

CS

CK

CKE

ODT

ZQ

DQS

DQ[7:0]

U11

CK

CS

CK

CKE

ODT

ZQ

DQS

DQ[7:0]

U20

CK

CS

CK

CKE

ODT

ZQ

DQS

DQ[7:0]

U29

CK

CS

CK

CKE

ODT

ZQ

DQS3

DQ[31:24]

DQS

DQ[7:0]

U3

CK

CS

CK

E

ODT

ZQ

DQS

DQ[7:0]

U12

CK

CS

CK

E

ODT

ZQ

DQS

DQ[7:0]

U21

CK

CS

CK

E

ODT

ZQ

DQS

DQ[7:0]

U30

CK

CS

CK

E

ODT

ZQ

DQS8

CB[7:0]

DQS

DQ[7:0]

U4

CK

CS

CK

E

ODT

ZQ

DQS

DQ[7:0]

U13

CK

CS

CK

E

ODT

ZQ

DQS

DQ[7:0]

U22

CK

CS

CK

E

ODT

ZQ

DQS

DQ[7:0]

U31

CK

CS

CK

E

ODT

ZQ

DQS4

DQ[39:32]

DQS

DQ[7:0]

U5

CK

CS

CK

E

ODT

ZQ

PCK

1

CS

0

PCK

1

E

C

KE0

EO

DT

0

DQS

DQ[7:0]

U14

CK

CS

CK

E

ODT

ZQ

PCK

1

CS

1

PCK

1

E

C

KE1

VDD

DQS

DQ[7:0]

U23

CK

CS

CK

E

ODT

ZQ

PCK

3

CS

2

PCK

3

E

C

KE0

EO

DT

1

DQS

DQ[7:0]

U32

CK

CS

CK

E

ODT

ZQ

PCK

3

CS

3

PCK

3

E

C

KE1

VDD

DQS5

DQ[47:40]

DQS

DQ[7:0]

U6

CK

CS

CK

E

ODT

ZQ

DQS

DQ[7:0]

U15

CK

CS

CK

E

ODT

ZQ

DQS

DQ[7:0]

U24

CK

CS

CK

E

ODT

ZQ

DQS6

DQ[55:48]

DQS

DQ[7:0]

U7

CK

CS

CK

CKE

ODT

ZQ

DQS

DQ[7:0]

U16

CK

CS

CK

CKE

ODT

ZQ

DQS

DQ[7:0]

U25

CK

CS

CK

CKE

ODT

ZQ

DQS

DQ[7:0]

U34

CK

CS

CK

CKE

ODT

ZQ

DQS3

DQ[31:24]

DQS

DQ[7:0]

U8

CK

CS

CK

E

OD

T

ZQ

DQS

DQ[7:0]

U17

CK

CS

CK

E

OD

T

ZQ

DQS

DQ[7:0]

U26

CK

CS

CK

E

OD

T

ZQ

DQS

DQ[7:0]

U35

CK

CS

CK

E

OD

T

ZQ

Vtt

VSS

VDD

D0 - D35

VREFCA

VDDSPD

Serial PD

VTT

VREFDQ

D0 - D35

NOTE :

1. DQ-to-I/O wiring may be changed within a nibble.

2. Unless otherwise noted, resistor values are 15

Ω ± 5%.

3. See the wiring diagrams for all resistors associated with the com-

mand, address and control bus.

4. ZQ resistors are 240

Ω ± 1% . For all other resistor values refer to

the appropriate wiring diagram.

A0

Thermal sensor with SPD

A1 A2

SA0 SA1 SA2

SCL

SDA

EVENT

Vtt

1:2

R

E

G

I

S

T

E

R

BA[N:0]

A[N:0]

RAS

CAS

WE

CKE0

RESET

RST : SDRAMs D[35:0]

PAR_IN

S0

RS0-> CS0 : SDRAMs D[8:0]

Err_out

QERR

RST

CK0

ODT0

CK0

S1

RS1-> CS1 : SDRAMs D[17:9]

RS2-> CS2 : SDRAMs D[26:18]

RS3-> CS3 : SDRAMs D[35:27]

WBA[N:0] -> BA[N:0]: SDRAMs D[4:0], D8, D[13:9], D[22:18], D[31:27]

EBA[N:0] -> BA[N:0]: SDRAMs D[8:5], D[17:14], D[26:23], D[35:32]

WA[N:0] -> A[N:0]: SDRAMs D[4:0], D8, D[13:9], D[22:18], D[31:27]

EA[N:0] -> A[N:0]: SDRAMs D[8:5], D[17:14], D[26:23], D[35:32]

WRAS -> RAS: SDRAMs D[4:0], D8, D[13:9], D[22:18], D[31:27]

ERAS -> RAS: SDRAMs D[8:5], D[17:14], D[26:23], D[35:32]

WCAS -> CAS: SDRAMs D[4:0], D8, D[13:9], D[22:18], D[31:27]

ECAS -> CAS: SDRAMs D[8:5], D[17:14], D[26:23], D[35:32]

WWE -> WE: SDRAMs D[4:0], D8, D[13:9], D[22:18], D[31:27]

EWE -> WE: SDRAMs D[8:5], D[17:14], D[26:23], D[35:32]

WCKE0 -> CKE0: SDRAMs D[4:0], D[22:18]

ECKE0 -> CKE0: SDRAMs D[8:5], D[26:23]

WODT0 -> ODT0: SDRAMs D[4:0]

EODT0 -> ODT0: SDRAMs D[8:5]

PCK0 -> CK: SDRAMs D[4:0], D[13:9]

PCK1 -> CK: SDRAMs D[8:5], D[26:23]

PCK2 -> CK: SDRAMs D[22:18], D[31:27]

PCK3 -> CK: SDRAMs D[17:14], D[35:32]

S2

S3

CKE1

WCKE1 -> CKE1: SDRAMs D[13:9], D[31:27]

ECKE1 -> CKE1: SDRAMs D[17:14], D[35:32]

ODT1

WODT1 -> ODT1: SDRAMs D[22:18]

EODT1 -> ODT1: SDRAMs D[26:23]

PCK0 -> CK: SDRAMs D[4:0], D[13:9]

PCK1 -> CK: SDRAMs D[8:5], D[26:23]

PCK2 -> CK: SDRAMs D[22:18], D[31:27]

PCK3 -> CK: SDRAMs D[17:14], D[35:32]

DQS

DQ[7:0]

U33

CK

CS

CK

E

ODT

ZQ

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M393B5773CH0-CK0 | 256M X 72 MULTI DEVICE DRAM MODULE, 0.225 ns, DMA240 |

| M3950/1529A012 | TOGGLE SWITCH, 3PDT, LATCHED, 4A, 28VDC, THROUGH HOLE-STRAIGHT |

| M83731/2327D110 | TOGGLE SWITCH, 3PDT, MOMENTARY, 4A, 28VDC, THROUGH HOLE-STRAIGHT |

| M3950/1726A110 | TOGGLE SWITCH, 3PDT, LATCHED, 4A, 28VDC, THROUGH HOLE-STRAIGHT |

| M3E-R21ZQXFREQ | CRYSTAL OSCILLATOR, CLOCK, 1.5 MHz - 155.52 MHz, PECL OUTPUT |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M393B5273CH0-CK004 | 制造商:Samsung 功能描述:4GBYTE REGISTERED DIMM, DDR3-1600 - Trays |

| M393B5273DH-CH9E8 | 制造商:Samsung Semiconductor 功能描述:4GB 2RX8 PC3-8500R-07-00-B0-D1 - Trays |

| M393B5670EH1 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:DDR3 SDRAM Memory |

| M393B5670EH1-CF801 | 制造商:Samsung Semiconductor 功能描述:2GB DDR3 REGISTERED DIMM, 1066MHZ, - Trays |

| M393B5670EH1-CH904 | 制造商:Samsung Semiconductor 功能描述:2GBYTE REGISTERED DIMM,DDR3-1333 - Trays |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。