- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄45050 > M48T18-150PC1 (STMICROELECTRONICS) 0 TIMER(S), REAL TIME CLOCK, PDIP28 PDF資料下載

參數(shù)資料

| 型號: | M48T18-150PC1 |

| 廠商: | STMICROELECTRONICS |

| 元件分類: | 時鐘/數(shù)據(jù)恢復(fù)及定時提取 |

| 英文描述: | 0 TIMER(S), REAL TIME CLOCK, PDIP28 |

| 封裝: | 0.600 INCH, ROHS COMPLIANT, PLASTIC, PCDIP-28 |

| 文件頁數(shù): | 4/31頁 |

| 文件大小: | 256K |

| 代理商: | M48T18-150PC1 |

第1頁第2頁第3頁當(dāng)前第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁

Operation modes

M48T08, M48T08Y, M48T18

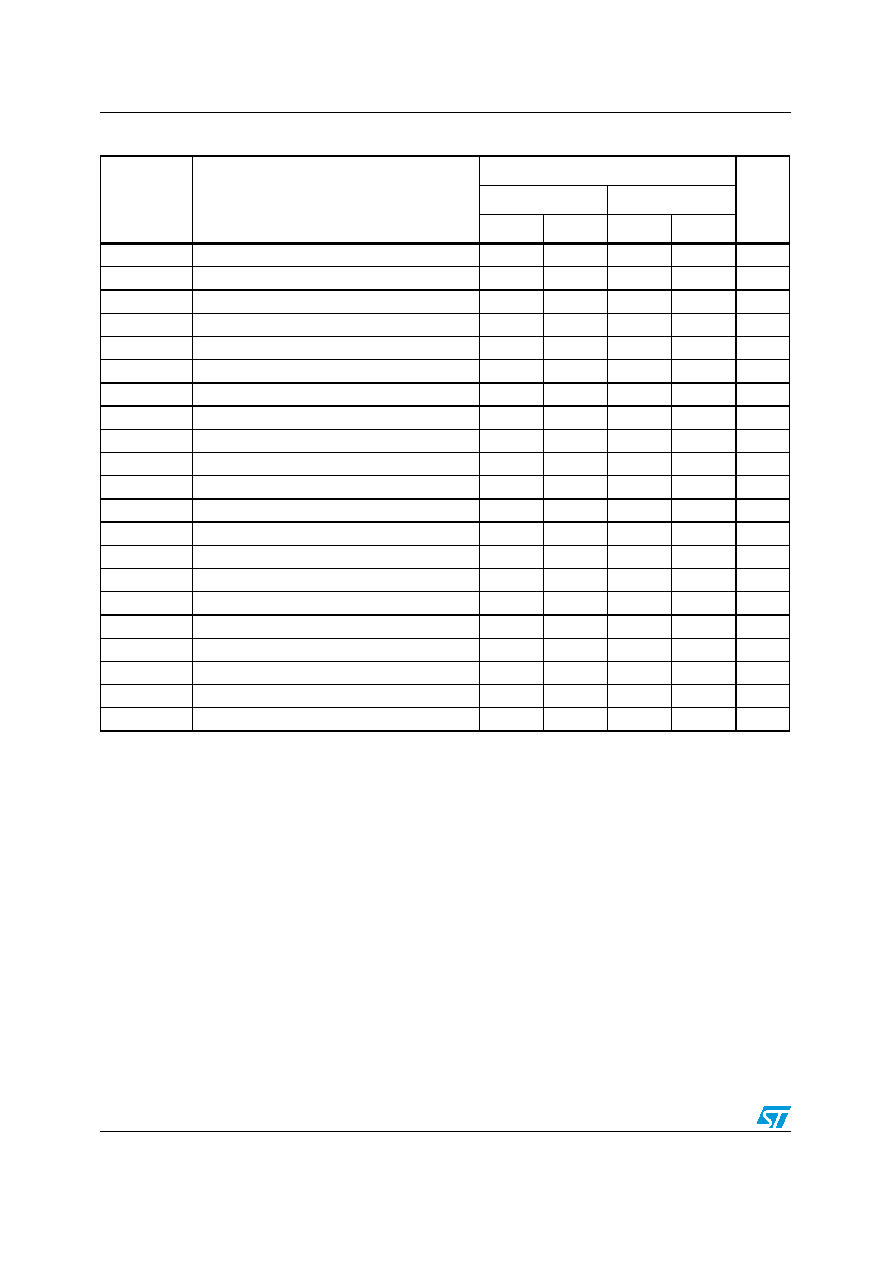

Table 4.

Write mode AC characteristics

2.3

Data retention mode

With valid VCC applied, the M48T08/18/08Y operates as a conventional BYTEWIDE static

RAM. Should the supply voltage decay, the RAM will automatically power-fail deselect, write

protecting itself when VCC falls within the VPFD (max), VPFD (min) window. All outputs

become high impedance, and all inputs are treated as “Don't care.”

Note:

A power failure during a WRITE cycle may corrupt data at the currently addressed location,

but does not jeopardize the rest of the RAM's content. At voltages below VPFD (min), the

user can be assured the memory will be in a write protected state, provided the VCC fall time

is not less than tF. The M48T08/18/08Y may respond to transient noise spikes on VCC that

reach into the deselect window during the time the device is sampling VCC. Therefore,

decoupling of the power supply lines is recommended.

Symbol

Parameter(1)

1.

Valid for ambient operating temperature: TA = 0 to 70°C; VCC = 4.75 to 5.5 V or 4.5 to 5.5 V (except where noted).

M48T08/M48T18/T08Y

Unit

–100/–10 (T08Y)

–150/–15 (T08Y)

MinMax

tAVAV

WRITE cycle time

100

150

ns

tAVWL

Address valid to WRITE enable low

0

ns

tAVE1L

Address valid to chip enable 1 low

0

ns

tAVE2H

Address valid to chip enable 2 high

0

ns

tWLWH

WRITE enable pulse width

80

100

ns

tE1LE1H

Chip enable 1 low to chip enable 1 high

80

130

ns

tE2HE2L

Chip enable 2 high to chip enable 2 low

80

130

ns

tWHAX

WRITE enable high to address transition

10

ns

tE1HAX

Chip enable 1 high to address transition

10

ns

tE2LAX

Chip enable 2 low to address transition

10

ns

tDVWH

Input valid to WRITE enable high

50

70

ns

tDVE1H

Input valid to chip enable 1 high

50

70

ns

tDVE2L

Input valid to chip enable 2 low

50

70

ns

tWHDX

WRITE enable high to input transition

5

ns

tE1HDX

Chip enable 1 high to input transition

5

ns

tE2LDX

Chip enable 2 low to input transition

5

ns

tWLQZ

WRITE enable low to output Hi-Z

50

70

ns

tAVWH

Address valid to WRITE enable high

80

130

ns

tAVE1H

Address valid to chip enable 1 high

80

130

ns

tAVE2L

Address valid to chip enable 2 low

80

130

ns

tWHQX

WRITE enable high to output transition

10

ns

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M48T08-100PC1 | 0 TIMER(S), REAL TIME CLOCK, PDIP28 |

| M48T08-150PC1 | 0 TIMER(S), REAL TIME CLOCK, PDIP28 |

| M48T18-100PC1 | 0 TIMER(S), REAL TIME CLOCK, PDIP28 |

| M48T201V-85MH1TR | 1 TIMER(S), REAL TIME CLOCK, PDSO44 |

| M48T201Y-70MH1F | 1 TIMER(S), REAL TIME CLOCK, PDSO44 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M48T18-150PC1E | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:64 Kbit 8Kb x 8 TIMEKEEPER SRAM |

| M48T18-150PC1F | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:64 Kbit 8Kb x 8 TIMEKEEPER SRAM |

| M48T18-150PC1TR | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:CMOS 8K x 8 TIMEKEEPER SRAM |

| M48T18MH | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:64 Kbit 8Kb x 8 TIMEKEEPER SRAM |

| M48T18PC | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:64 Kbit 8Kb x 8 TIMEKEEPER SRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。