- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359070 > M48Z35AY-70MH6TR (意法半導(dǎo)體) 256 Kbit 32Kb x8 ZEROPOWER SRAM PDF資料下載

參數(shù)資料

| 型號: | M48Z35AY-70MH6TR |

| 廠商: | 意法半導(dǎo)體 |

| 英文描述: | 256 Kbit 32Kb x8 ZEROPOWER SRAM |

| 中文描述: | 256千位的32KB的SRAM x8 ZEROPOWER |

| 文件頁數(shù): | 8/18頁 |

| 文件大小: | 135K |

| 代理商: | M48Z35AY-70MH6TR |

M48Z35, M48Z35Y

8/18

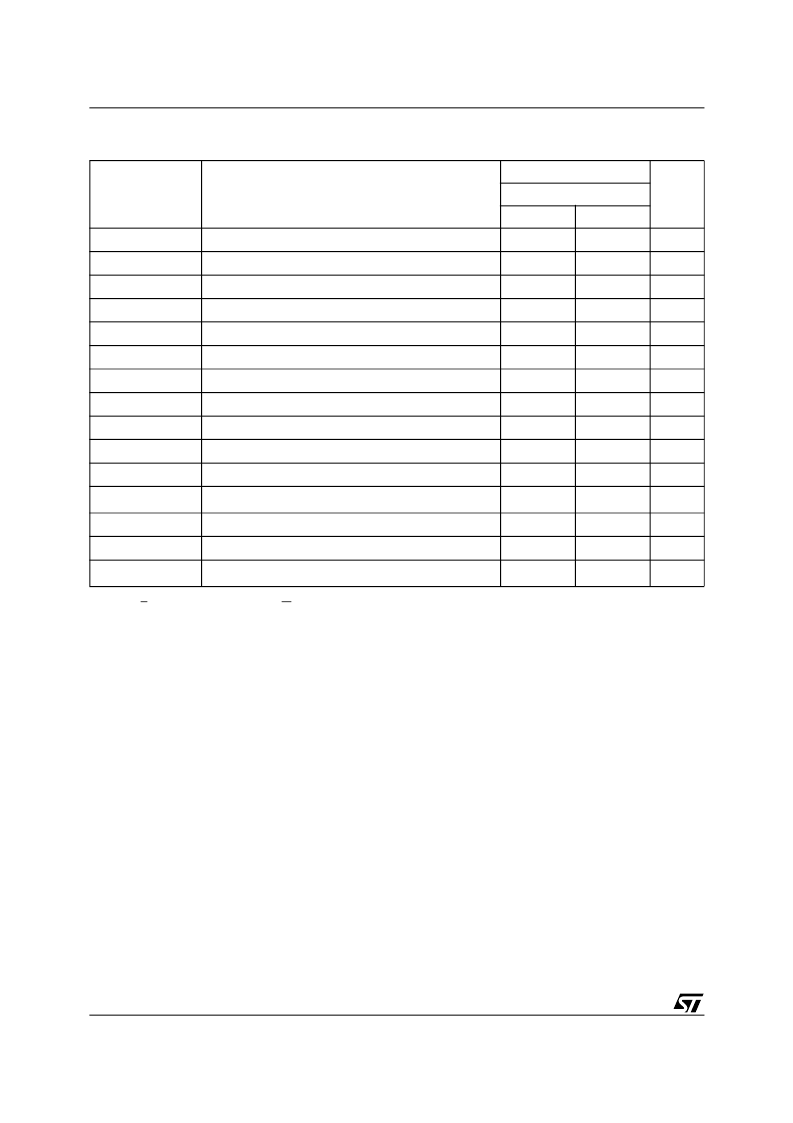

Table 10. Write Mode AC Characteristics

(T

A

= 0 to 70 °C or –40 to 85 °C; V

CC

= 4.75V to 5.5V or 4.5V to 5.5V)

Note: 1. C

L

= 5pF (see Figure 4).

2. If E goes low simultaneously with W going low, the outputs remain in the high impedance state.

Symbol

Parameter

M48Z35 / M48Z35Y

Unit

-70

Min

Max

t

AVAV

Write Cycle Time

70

ns

t

AVWL

Address Valid to Write Enable Low

0

ns

t

AVEL

Address Valid to Chip Enable Low

0

ns

t

WLWH

Write Enable Pulse Width

50

ns

t

ELEH

Chip Enable Low to Chip Enable High

55

ns

t

WHAX

Write Enable High to Address Transition

0

ns

t

EHAX

Chip Enable High to Address Transition

0

ns

t

DVWH

Input Valid to Write Enable High

30

ns

t

DVEH

Input Valid to Chip Enable High

30

ns

t

WHDX

Write Enable High to Input Transition

5

ns

t

EHDX

Chip Enable High to Input Transition

5

ns

t

WLQZ

(1, 2)

Write Enable Low to Output Hi-Z

25

ns

t

AVWH

Address Valid to Write Enable High

60

ns

t

AVEH

Address Valid to Chip Enable High

60

ns

t

WHQX

(1, 2)

Write Enable High to Output Transition

5

ns

DATA RETENTION MODE

With valid V

CC

applied, the M48Z35/35Y operates

as a conventional BYTEWIDE static RAM.

Should the supply voltage decay, the RAM will au-

tomatically power-fail deselect, write protecting it-

self when V

CC

falls within the V

PFD

(max),

V

PFD

(min) window. All outputs become high im-

pedance, and all inputs are treated as "don't care."

Note:

A power failure during a write cycle may cor-

rupt data at the currently addressed location, but

does not jeopardize the rest of the RAM's content.

At voltages below V

PFD

(min), the user can be as-

sured the memory will be in a write protected state,

provided the V

CC

fall time is not less than t

F

. The

M48Z35/35Y may respond to transient noise

spikes on V

CC

that reach into the deselect window

during the time the device is sampling V

CC

. There-

fore, decoupling of the power supply lines is rec-

ommended.

When V

CC

drops below V

SO

, the control circuit

switches power to the internal battery which pre-

serves data. The internal button cell will maintain

data in the M48Z35/35Y for an accumulated peri-

od of at least 10 years (at 25°C) when V

CC

is less

than V

SO

.

As system power returns and V

CC

rises above

V

SO

, the battery is disconnected, and the power

supply is switched to external V

CC

. Write protec-

tion continues until V

CC

reaches V

PFD

(min) plus

t

REC

(min). Normal RAM operation can resume

t

REC

after V

CC

exceeds V

PFD

(max).

For more information on Battery Storage Life refer

to the Application Note AN1012.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M48Z35AY-70PC1 | 256 Kbit 32Kb x8 ZEROPOWER SRAM |

| M48Z35AY-70PC1TR | 256 Kbit 32Kb x8 ZEROPOWER SRAM |

| M48Z512AYCS | 4 Mbit 512Kb x8 ZEROPOWER SRAM |

| M48Z512AY-85CS9 | 4 Mbit 512Kb x8 ZEROPOWER SRAM |

| M48Z512AY-70CS9 | 4 Mbit 512Kb x8 ZEROPOWER SRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M48Z35AY-70PC1 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:256 Kbit 32Kb x8 ZEROPOWER SRAM |

| M48Z35AY-70PC1TR | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:256 Kbit 32Kb x8 ZEROPOWER SRAM |

| M48Z35AY-70PC6 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:256 Kbit 32Kb x8 ZEROPOWER SRAM |

| M48Z35AY-70PC6TR | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:256 Kbit 32Kb x8 ZEROPOWER SRAM |

| M48Z35AYMH | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:256 Kbit 32Kb x8 ZEROPOWER SRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。