- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359070 > M48Z512AY-85CS9 (意法半導體) 4 Mbit 512Kb x8 ZEROPOWER SRAM PDF資料下載

參數(shù)資料

| 型號: | M48Z512AY-85CS9 |

| 廠商: | 意法半導體 |

| 英文描述: | 4 Mbit 512Kb x8 ZEROPOWER SRAM |

| 中文描述: | 4兆位的SRAM 512KB的x8 ZEROPOWER |

| 文件頁數(shù): | 11/17頁 |

| 文件大小: | 101K |

| 代理商: | M48Z512AY-85CS9 |

11/17

M48Z512A, M48Z512AY

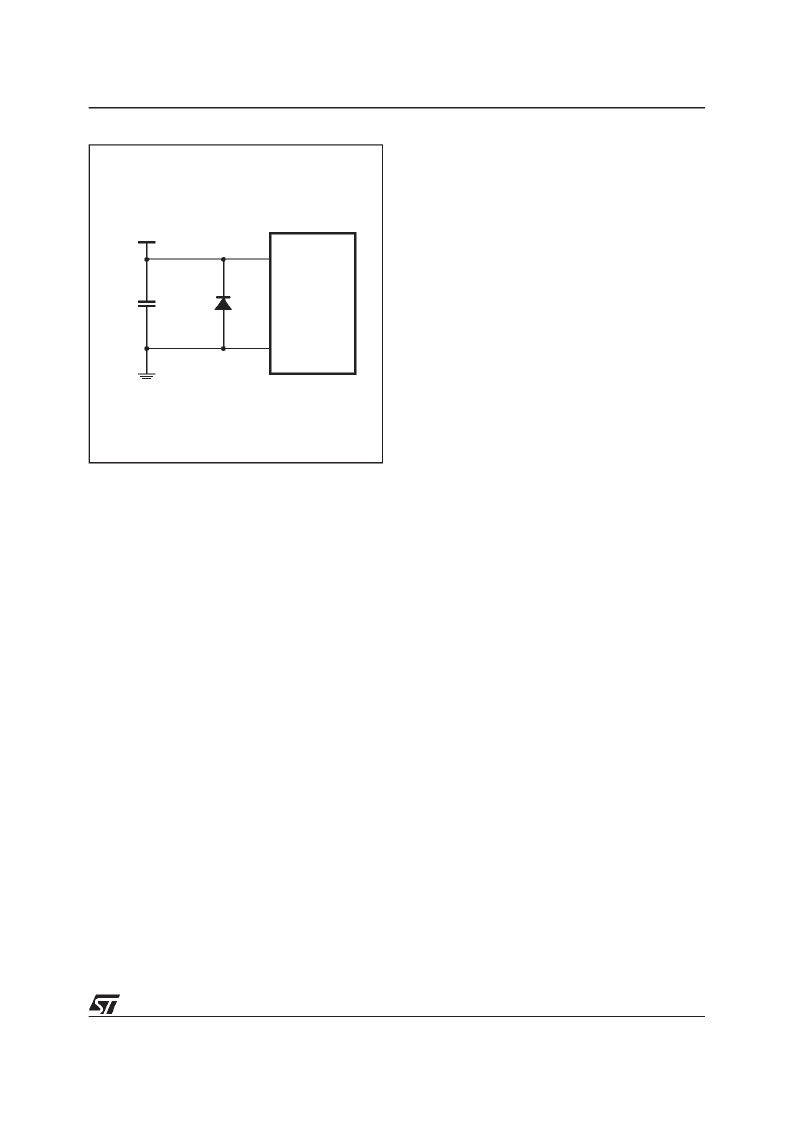

Figure 11. Supply Voltage Protection

AI02169

VCC

0.1

μ

F

DEVICE

VCC

VSS

DATA RETENTION MODE

With valid V

CC

applied, the M48Z512A/512AY op-

erates as a conventional BYTEWIDE

static

RAM. Should the supply voltage decay, the RAM

will automatically power-fail deselect, write pro-

tecting itself t

WP

after V

CC

falls below V

PFD

. All

outputs become high impedance, and all inputs

are treated as ”don’t care.”

If power fail detection occurs during a valid ac-

cess, thememory cycle continues to completion. If

the memory cycle fails to terminate within the time

t

WP

, writeprotection takes place. When V

CC

drops

below V

SO

, the control circuit switches power to

the internal energy source which preserves data.

The internal coin cell will maintain data in the

M48Z512A/512AY after the initial application of

V

CC

for an accumulated period of at least 10 years

when V

CC

is less than V

SO

. As system power re-

turns and V

CC

rises above V

SO

, the battery is dis-

connected, and the power supply is switched to

external V

CC

. Writeprotection continues for t

ER

af-

ter V

CC

reaches V

PFD

to allow for processor stabi-

lization. After t

ER

, normal RAM operation can

resume.

For more information on Battery Storage Life refer

to the Application Note AN1012.

POWER SUPPLY DECOUPLING

and UNDERSHOOT PROTECTION

I

CC

transients, including those produced by output

switching, can produce voltage fluctuations, re-

sulting in spikes on the V

CC

bus. These transients

can be reduced if capacitors are used to store en-

ergy, which stabilizes the V

CC

bus. The energy

stored in the bypass capacitors will be released as

low going spikes are generated or energy will be

absorbed when overshoots occur. A ceramic by-

pass capacitor value of 0.1

μ

F (as shown in Figure

11) is recommended in order to provide the need-

ed filtering.

In addition to transients that are caused by normal

SRAM operation, power cycling cangenerate neg-

ative voltage spikes on V

CC

that drive it to values

below V

SS

by as much as one Volt. These nega-

tive spikes can cause data corruptionin the SRAM

while in battery backup mode. To protect from

these voltage spikes, itis recommeded to connect

a schottky diode from V

CC

to V

SS

(cathode con-

nected to V

CC

, anode to V

SS

). Schottky diode

1N5817 is recommended for through hole and

MBRS120T3 is recommended for surface mount.

相關PDF資料 |

PDF描述 |

|---|---|

| M48Z512AY-70CS9 | 4 Mbit 512Kb x8 ZEROPOWER SRAM |

| M48Z512AY-70PM1 | 4 Mbit 512Kb x8 ZEROPOWER SRAM |

| M48Z512AY-70PM9 | 4 Mbit 512Kb x8 ZEROPOWER SRAM |

| M48Z512AY-85PM1 | 4 Mbit 512Kb x8 ZEROPOWER SRAM |

| M48Z512AY-85PM9 | 4 Mbit 512Kb x8 ZEROPOWER SRAM |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| M48Z512AY-85PM1 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:4 Mbit (512 Kbit x 8) ZEROPOWER SRAM |

| M48Z512AY-85PM6 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:4 Mbit (512 Kbit x 8) ZEROPOWER SRAM |

| M48Z512AY-85PM9 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:4 Mbit 512Kb x8 ZEROPOWER SRAM |

| M48Z512AYCS | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:4 Mbit 512Kb x8 ZEROPOWER SRAM |

| M48Z512AYPM | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:4 Mbit 512Kb x8 ZEROPOWER SRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復。