- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄180221 > M4A3-256/128-10VI (LATTICE SEMICONDUCTOR CORP) High Performance E 2 CMOS In-System Programmable Logic PDF資料下載

參數(shù)資料

| 型號(hào): | M4A3-256/128-10VI |

| 廠商: | LATTICE SEMICONDUCTOR CORP |

| 元件分類(lèi): | PLD |

| 英文描述: | High Performance E 2 CMOS In-System Programmable Logic |

| 中文描述: | EE PLD, 10 ns, PQFP176 |

| 封裝: | TQFP-176 |

| 文件頁(yè)數(shù): | 8/61頁(yè) |

| 文件大小: | 1169K |

| 代理商: | M4A3-256/128-10VI |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)當(dāng)前第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)

16

MACH 4 Family

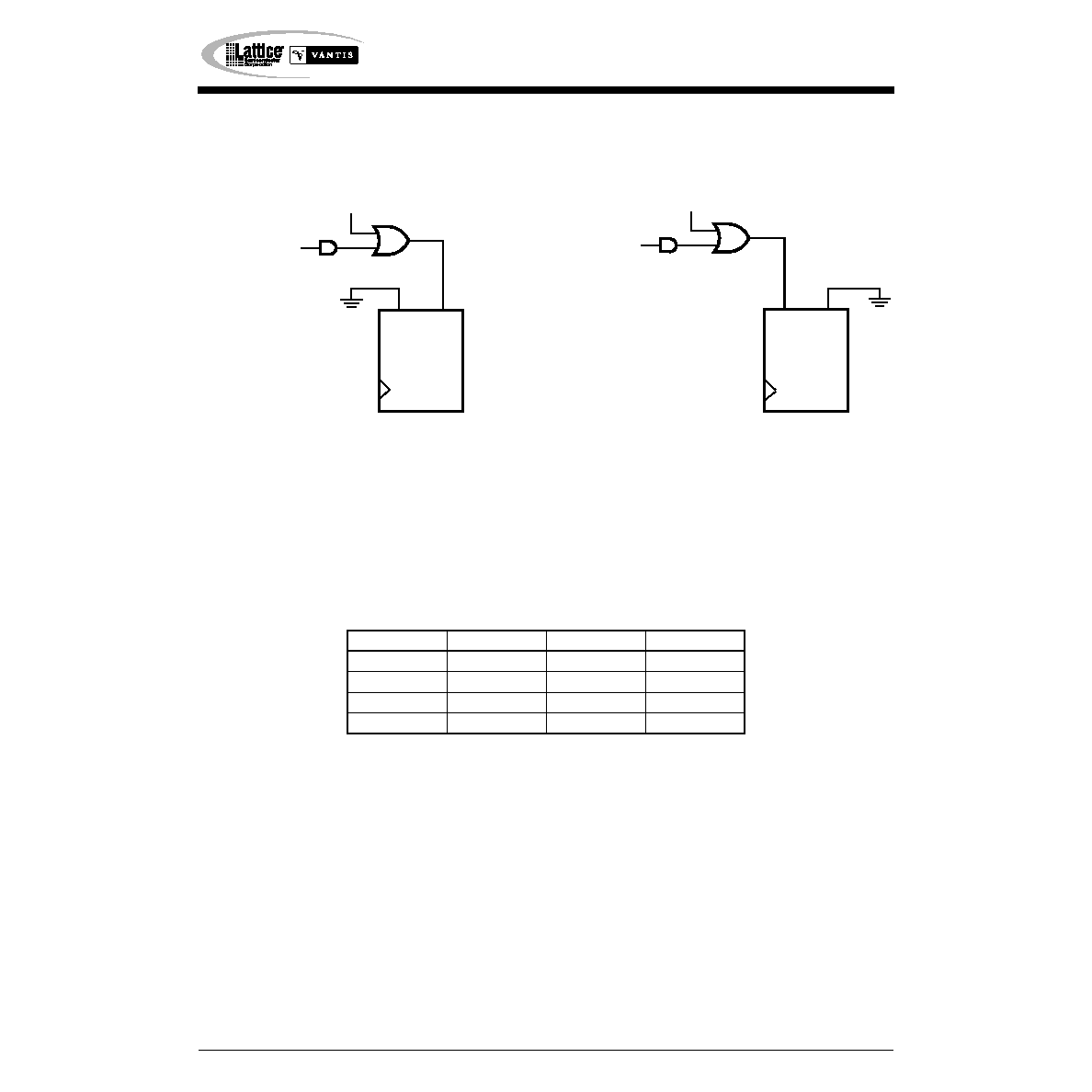

A reset/preset swapping feature in each macrocell allows for reset and preset to be exchanged,

providing exibility. In asynchronous mode (Figure 8), a single individual product term is

provided for initialization. It can be selected to control reset or preset.

Note that the reset/preset swapping selection feature effects power-up reset as well. The

initialization functionality of the ip-ops is illustrated in Table 13. The macrocell sends its data

to the output switch matrix and the input switch matrix. The output switch matrix can route this

data to an output if so desired. The input switch matrix can send the signal back to the central

switch matrix as feedback.

Note:

1. Transparent latch is unaffected by AR, AP

Output Switch Matrix

The output switch matrix allows macrocells to be connected to any of several I/O cells within a

PAL block. This provides high exibility in determining pinout and allows design changes to

occur without effecting pinout.

In MACH 4 and MACH 4A devices with 2:1 Macrocell-I/O cell ratio, each PAL block has twice as

many macrocells as I/O cells. The MACH 4 output switch matrix allows for half of the macrocells

to drive I/O cells within a PAL block, in combinations according to Figure 9. Each I/O cell can

choose from eight macrocells; each macrocell has a choice of four I/O cells. The MACH 4 and

MACH 4A devices with 1:1 Macrocell-I/O cell ratio allow each macrocell to drive one of eight

I/O cells (Figure 9).

Table 13. Asynchronous Reset/Preset Operation

AR

AP

CLK/LE1

Q+

0

X

See Table 12

01X1

10X0

11X0

Power-Up

Reset

AP

D/L/T

AR

Q

Individual

Reset

Product Term

a. Reset

Power-Up

Preset

AP

D/L/T

AR

Q

Individual

Preset

Product Term

b. Preset

17466G-014

17466G-015

Figure 8. Asynchronous Mode Initialization Congurations

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M4A3-256/128-7VI | CAP 1500UF 100V ELECT KMH SNAP |

| M4A3-384/192-10AC | High Performance E 2 CMOS In-System Programmable Logic |

| M4A3-384/192-10AI | High Performance E 2 CMOS In-System Programmable Logic |

| M4A3-384/192-14AI | High Performance E 2 CMOS In-System Programmable Logic |

| M4A3-384/192-65AC | High Performance E 2 CMOS In-System Programmable Logic |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M4A3-32/32-10JC | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 HI PERF E2CMOS PLD RoHS:否 制造商:Lattice 系列: 存儲(chǔ)類(lèi)型:EEPROM 大電池?cái)?shù)量:128 最大工作頻率:333 MHz 延遲時(shí)間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| M4A3-32/32-10JI | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 HI PERF E2CMOS PLD RoHS:否 制造商:Lattice 系列: 存儲(chǔ)類(lèi)型:EEPROM 大電池?cái)?shù)量:128 最大工作頻率:333 MHz 延遲時(shí)間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| M4A3-32/32-10JNC | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 Use ispMACH 4000V RoHS:否 制造商:Lattice 系列: 存儲(chǔ)類(lèi)型:EEPROM 大電池?cái)?shù)量:128 最大工作頻率:333 MHz 延遲時(shí)間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| M4A3-32/32-10JNI | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 Use ispMACH 4000V RoHS:否 制造商:Lattice 系列: 存儲(chǔ)類(lèi)型:EEPROM 大電池?cái)?shù)量:128 最大工作頻率:333 MHz 延遲時(shí)間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| M4A3-32/32-10VC | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 HI PERF E2CMOS PLD RoHS:否 制造商:Lattice 系列: 存儲(chǔ)類(lèi)型:EEPROM 大電池?cái)?shù)量:128 最大工作頻率:333 MHz 延遲時(shí)間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。