- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄180220 > M4A3-256/128-7YC (LATTICE SEMICONDUCTOR CORP) High Performance E 2 CMOS In-System Programmable Logic PDF資料下載

參數(shù)資料

| 型號: | M4A3-256/128-7YC |

| 廠商: | LATTICE SEMICONDUCTOR CORP |

| 元件分類: | PLD |

| 英文描述: | High Performance E 2 CMOS In-System Programmable Logic |

| 中文描述: | EE PLD, 7.5 ns, PQFP208 |

| 封裝: | PLASTIC, QFP-208 |

| 文件頁數(shù): | 9/62頁 |

| 文件大小: | 1078K |

| 代理商: | M4A3-256/128-7YC |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁當(dāng)前第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁

ispMACH 4A Family

17

I/O Cell

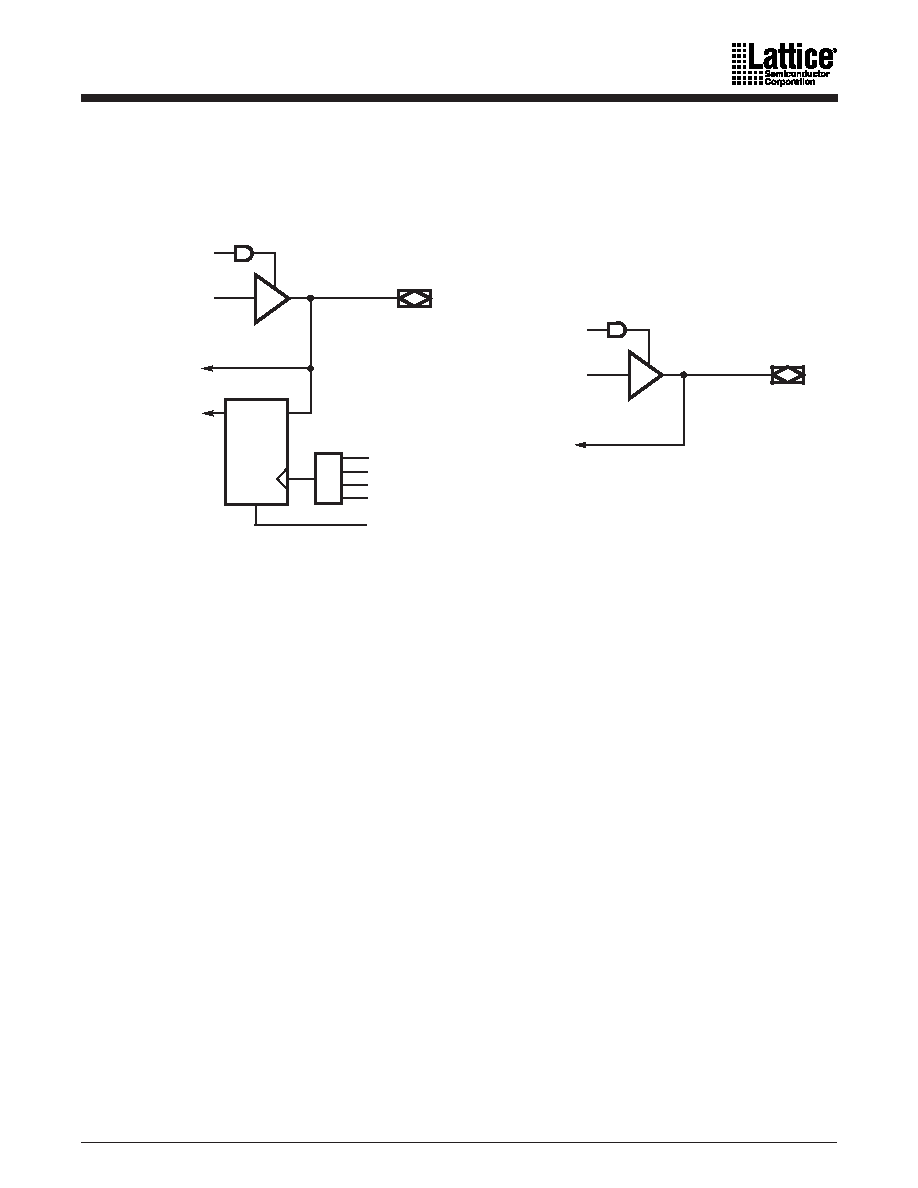

The I/O cell (Figures 10 and 11) simply consists of a programmable output enable, a feedback path, and

flip-flop (except ispMACH 4A devices with 1:1 macrocell-I/O cell ratio). An individual output enable

product term is provided for each I/O cell. The feedback signal drives the input switch matrix.

The I/O cell (Figure 10) contains a flip-flop, which provides the capability for storing the input in a D-type

register or latch. The clock can be any of the PAL block clocks. Both the direct and registered versions of

the input are sent to the input switch matrix. This allows for such functions as “time-domain-multiplexed”

data comparison, where the first data value is stored, and then the second data value is put on the I/O pin

and compared with the previous stored value.

Note that the flip-flop used in the ispMACH 4A I/O cell is independent of the flip-flops in the macrocells.

It powers up to a logic low.

Zero-Hold-Time Input Register

The ispMACH 4A devices have a zero-hold-time (ZHT) fuse which controls the time delay associated with

loading data into all I/O cell registers and latches. When programmed, the ZHT fuse increases the data path

setup delays to input storage elements, matching equivalent delays in the clock path. When the fuse is erased,

the setup time to the input storage element is minimized. This feature facilitates doing worst-case designs

for which data is loaded from sources which have low (or zero) minimum output propagation delays from

clock edges.

D/L

Q

Block CLK3

Block CLK2

Block CLK1

Block CLK0

To Input

Switch

Matrix

Individual

Output Enable

Product Term

From Output

Switch Matrix

17466G-017

17466G-018

Figure 10. I/O Cell for ispMACH 4A Devices with 2:1

Macrocell-I/O Cell Ratio

Figure 11. I/O Cell for ispMACH 4A Devices with 1:1

Macrocell-I/O Cell Ratio

To Input

Switch

Matrix

Individual

Output Enable

Product Term

From Output

Switch Matrix

Power-up reset

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M4A3-32/32-7JC | High Performance E 2 CMOS In-System Programmable Logic |

| M4A3-32/32-7JI | High Performance E 2 CMOS In-System Programmable Logic |

| M4A3-32/32-7VC | High Performance E 2 CMOS In-System Programmable Logic |

| M4A3-32/32-7VI | High Performance E 2 CMOS In-System Programmable Logic |

| M4A3-64/32-55JC | High Performance E 2 CMOS In-System Programmable Logic |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M4A3-32/32-10JC | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 HI PERF E2CMOS PLD RoHS:否 制造商:Lattice 系列: 存儲類型:EEPROM 大電池數(shù)量:128 最大工作頻率:333 MHz 延遲時間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| M4A3-32/32-10JI | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 HI PERF E2CMOS PLD RoHS:否 制造商:Lattice 系列: 存儲類型:EEPROM 大電池數(shù)量:128 最大工作頻率:333 MHz 延遲時間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| M4A3-32/32-10JNC | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 Use ispMACH 4000V RoHS:否 制造商:Lattice 系列: 存儲類型:EEPROM 大電池數(shù)量:128 最大工作頻率:333 MHz 延遲時間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| M4A3-32/32-10JNI | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 Use ispMACH 4000V RoHS:否 制造商:Lattice 系列: 存儲類型:EEPROM 大電池數(shù)量:128 最大工作頻率:333 MHz 延遲時間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| M4A3-32/32-10VC | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 HI PERF E2CMOS PLD RoHS:否 制造商:Lattice 系列: 存儲類型:EEPROM 大電池數(shù)量:128 最大工作頻率:333 MHz 延遲時間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。