- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄180220 > M4A5-192/96-6VC (LATTICE SEMICONDUCTOR CORP) High Performance E 2 CMOS In-System Programmable Logic PDF資料下載

參數(shù)資料

| 型號: | M4A5-192/96-6VC |

| 廠商: | LATTICE SEMICONDUCTOR CORP |

| 元件分類: | PLD |

| 英文描述: | High Performance E 2 CMOS In-System Programmable Logic |

| 中文描述: | EE PLD, 6 ns, PQFP144 |

| 封裝: | TQFP-144 |

| 文件頁數(shù): | 4/62頁 |

| 文件大小: | 1078K |

| 代理商: | M4A5-192/96-6VC |

第1頁第2頁第3頁當(dāng)前第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁

12

ispMACH 4A Family

Note:

1. Polarity of CLK/LE can be programmed

Although the macrocell shows only one input to the register, the XOR gate in the logic allocator allows the

D-, T-type register to emulate J-K, and S-R behavior. In this case, the available product terms are divided

between J and K (or S and R). When configured as J-K, S-R, or T-type, the extra product term must be used

on the XOR gate input for flip-flop emulation. In any register type, the polarity of the inputs can be

programmed.

The clock input to the flip-flop can select any of the four PAL block clocks in synchronous mode, with the

additional choice of either polarity of an individual product term clock in the asynchronous mode.

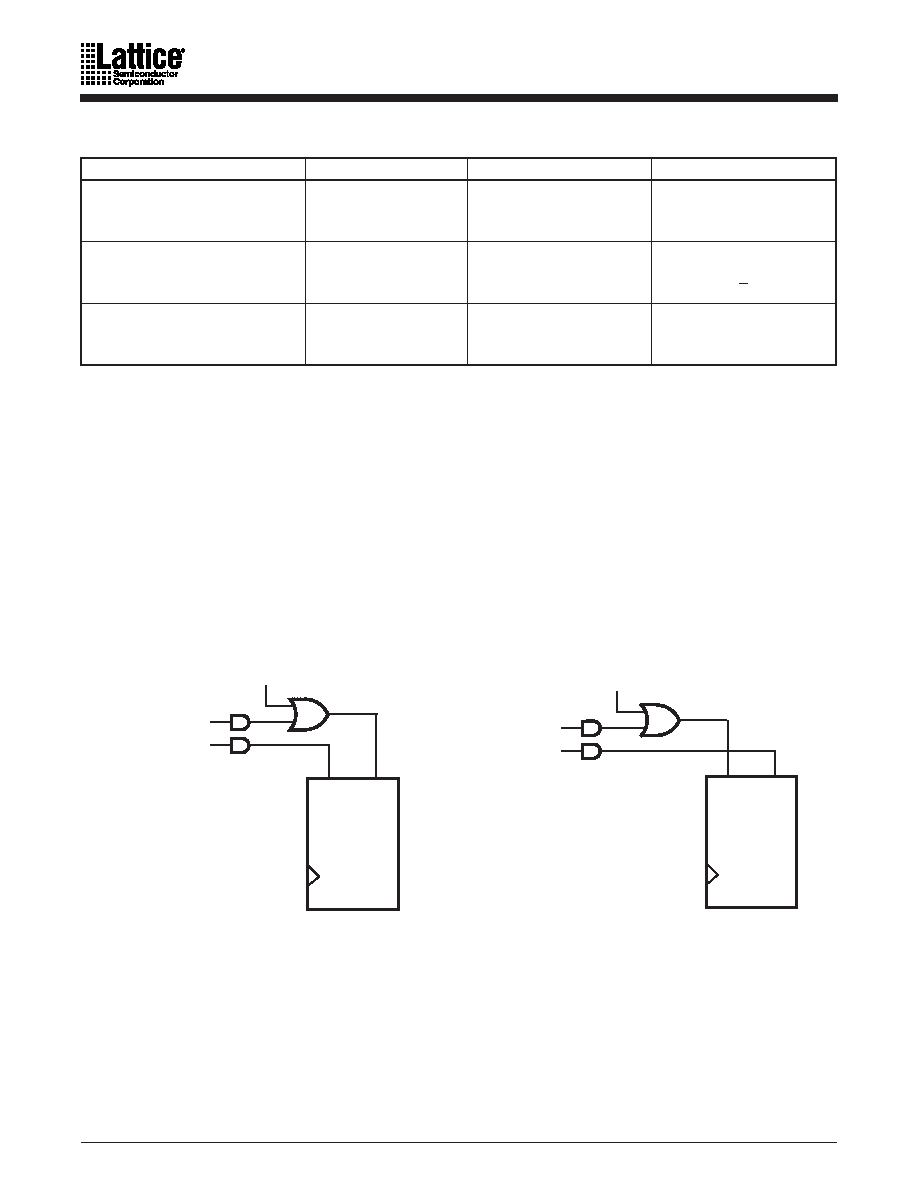

The initialization circuit depends on the mode. In synchronous mode (Figure 7), asynchronous reset and

preset are provided, each driven by a product term common to the entire PAL block.

Table 8. Register/Latch Operation

Conguration

Input(s)

CLK/LE 1

Q+

D-type Register

D=X

D=0

D=1

0,1, ↓ (↑)

↑ (↓)

Q

0

1

T-type Register

T=X

T=0

T=1

0, 1, ↓ (↑)

↑ (↓)

Q

D-type Latch

D=X

D=0

D=1

1(0)

0(1)

Q

0

1

Power-Up

Reset

AP

D/T/L

AR

Q

PAL-Block

Initialization

Product Terms

a. Power-up reset

Power-Up

Preset

AP

D/L

PAL-Block

Initialization

Product Terms

AR

Q

17466G-012

17466G-013

Figure 7. Synchronous Mode Initialization Congurations

b. Power-up preset

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M4A5-192/96-7VC | High Performance E 2 CMOS In-System Programmable Logic |

| M4A5-192/96-7VI | High Performance E 2 CMOS In-System Programmable Logic |

| M4A5-256/128-65YC | High Performance E 2 CMOS In-System Programmable Logic |

| M4A5-256/128-7YC | High Performance E 2 CMOS In-System Programmable Logic |

| M4A5-32/32-12JI | High Performance E 2 CMOS In-System Programmable Logic |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M4A5-256/128-10AC | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:High Performance E 2 CMOS In-System Programmable Logic |

| M4A5-256/128-10YC | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 HI PERF E2CMOS PLD RoHS:否 制造商:Lattice 系列: 存儲類型:EEPROM 大電池數(shù)量:128 最大工作頻率:333 MHz 延遲時間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| M4A5-256/128-10YI | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 HI PERF E2CMOS PLD RoHS:否 制造商:Lattice 系列: 存儲類型:EEPROM 大電池數(shù)量:128 最大工作頻率:333 MHz 延遲時間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| M4A5-256/128-10YNC | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 HI PERF E2CMOS PLD RoHS:否 制造商:Lattice 系列: 存儲類型:EEPROM 大電池數(shù)量:128 最大工作頻率:333 MHz 延遲時間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| M4A5-256/128-10YNI | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 HI PERF E2CMOS PLD RoHS:否 制造商:Lattice 系列: 存儲類型:EEPROM 大電池數(shù)量:128 最大工作頻率:333 MHz 延遲時間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。