- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370973 > M5M4V16169DTP (Mitsubishi Electric Corporation) 16MCDRAM:16M(1M-WORD BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM PDF資料下載

參數(shù)資料

| 型號(hào): | M5M4V16169DTP |

| 廠商: | Mitsubishi Electric Corporation |

| 英文描述: | 16MCDRAM:16M(1M-WORD BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM |

| 中文描述: | 16MCDRAM:16米(100萬字由16位)與16K的緩存內(nèi)存(1024字由16位)的SRAM |

| 文件頁數(shù): | 17/64頁 |

| 文件大?。?/td> | 737K |

| 代理商: | M5M4V16169DTP |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁當(dāng)前第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁

M5M4V16169DTP/RT-7,-8,-10,-15

16MCDRAM:16M(1M-WORD BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM

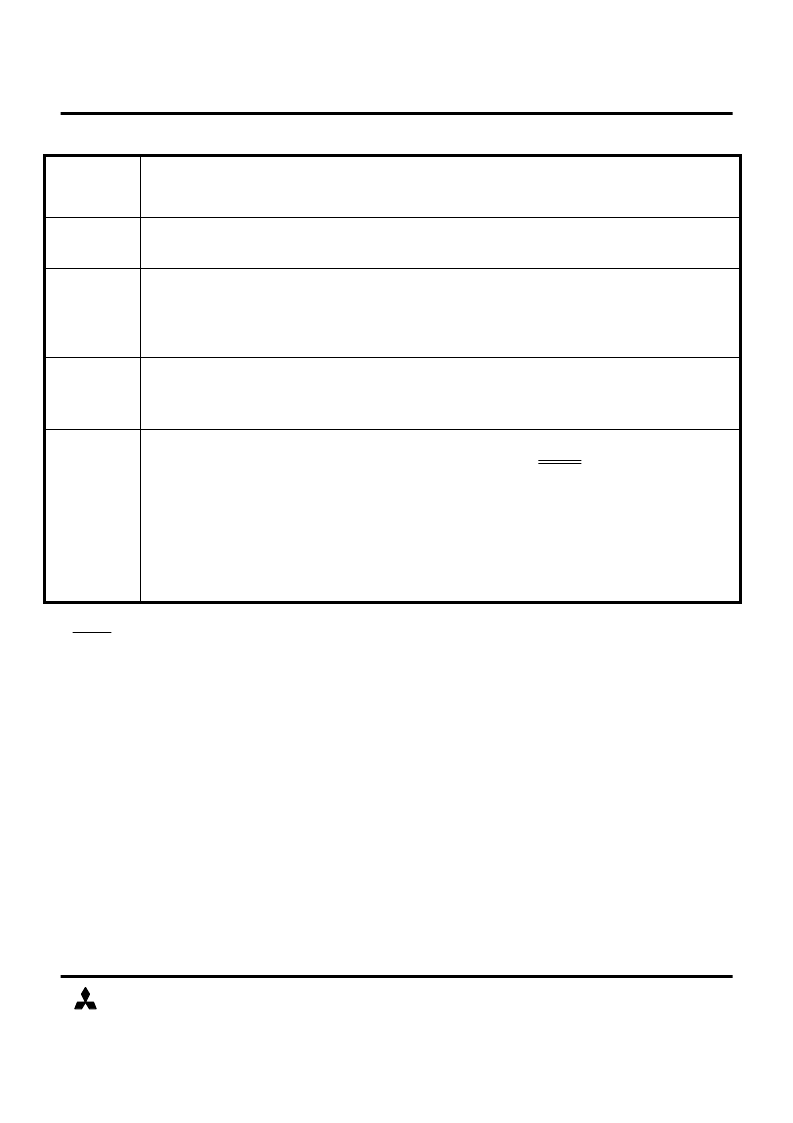

MODE DESCRIPTIONS (10)

MITSUBISHI LSIs

(REV 1.0) Jul. 1998

MITSUBISHI ELECTRIC

Notes:

1)

This function is performed in a Latency period specified in the Access Latency Table.

2)

After the Latency Period (specified in the Access Latency Table) new data will be present

in the Read Buffer2. Prior to the Latency timeout, old data will be present in the RB2.

3)

After data has been transferred from WB1, the entire WB1 Mask is Set.

4)

Valid Ad0-Ad2 addresses are shown in the FUNCTION TRUTH TABLE.

DRAM

Activate

DRAM

Precharge

DRAM

Auto-Refresh

DRAM

Self Refresh

Addresses are latched from the Ad0-Ad11 inputs by the rising edge of K. Internally, a DRAM row is

selected (Page Call) in preparation for a DRAM Read or Write Transfer cycle. A DRAM Precharge

cycle must separate all DRAM Activate cycles.

Internally, the active DRAM Row is deselected (completing the refresh process) and page-mode is

disabled. The DRAM is precharged prior to another DRAM Activate cycle.

Internally, a DRAM row is selected and refreshed (as addressed by an internal, self-incrementing

counter), followed by an internally generated Precharge cycle. The Auto refresh cycle can be

implemented only if the DRAM is in Precharge state (i.e., a Precharge or Auto-Refresh cycle

occurred more recently than an Acitvate cycle). DRAM Auto-Refresh is similar to a CAS-Before-

RAS (CBR) mode in standard DRAMs.

All clock buffers are suspended, and CMd# asynchronously controls Self Refresh (CMd# rising

edge initiates exit from Self Refresh). During Self Refresh, device enters a low power mode, with

2048 automatic refresh cycles.

Set

Command

Register

When SCR is initiated,the addresses present on the Ad0-Ad11 DRAM Address pins determine the

DRAM Read Transfer Latency, the Output Mode (transparent / latched / registered), and WB1

transfer mask mode (set-all/ no change). No DRAM operation is executed in this cycle. Refer to

the SCR Truth Table for legal Address values.

During SCR cycle and the following 3 clock cycles(totally 4 clock cycles), only NOP,DNOP orDPD

are allowed in DRAM portion and only NOP,DES or SPD are done in SRAM portion. The set

commands are valid at least after the above 4 clocks later and the previous function is not

guaranteed to work if it has not been completed.(i.e. DRT ,DWT1&R,DWT2&R and SR,BR and

BRTR with registered output mode.)

17

Power-On sequence

Before starting normal operation, the following power on sequence is necessary.

1) Apply power and maintain stable power (pause) for 500us.

2) Perform a precharge (PCG) operation.

3) After tRP, perform 8 auto refresh commands (ARF) with adequate interval (tRC).

4) Issue set command register (SCR) to initilize the mode register.

After this sequence, the RAM is in idle state and ready for normal operation.

Note that DNOP / DPD and DES / SPD or NOP command will be the stand-by command

for the above power sequence.

Vcc must be powered-on at the same time or before VccQ is on.

And Vcc must be powered-off at the same time or after VccQ is off.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M5M4V16169DRT-10 | 16MCDRAM:16M(1M-WORD BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM |

| M5M4V16169DRT-15 | 16MCDRAM:16M(1M-WORD BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM |

| M5M4V16169DRT-7 | 16MCDRAM:16M(1M-WORD BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM |

| M5M4V16169DRT-8 | 22182053 |

| M5M4V16G50DFP-10 | 16M (2-BANK x 262144-WORD x 32-BIT) Synchronous Graphics RAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M5M4V16169DTP-10 | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:16MCDRAM:16M(1M-WORD BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM |

| M5M4V16169DTP-15 | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:16MCDRAM:16M(1M-WORD BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM |

| M5M4V16169DTP-7 | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:16MCDRAM:16M(1M-WORD BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM |

| M5M4V16169DTP-8 | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:16MCDRAM:16M(1M-WORD BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM |

| M5M4V16G50DFP-10 | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:16M (2-BANK x 262144-WORD x 32-BIT) Synchronous Graphics RAM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。