- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359088 > M68AW064F (意法半導(dǎo)體) CAC 6C 6#16S PIN PLUG PDF資料下載

參數(shù)資料

| 型號(hào): | M68AW064F |

| 廠商: | 意法半導(dǎo)體 |

| 英文描述: | CAC 6C 6#16S PIN PLUG |

| 中文描述: | 1兆位64K的x16 3.0V異步SRAM |

| 文件頁數(shù): | 11/18頁 |

| 文件大?。?/td> | 265K |

| 代理商: | M68AW064F |

11/18

M68AW064F

Write Mode

The M68AW064F is in the Write mode whenever

the W and E are Low. Either the Chip Enable input

(E) or the Write Enable input (W) must be de-

asserted

during

Address

subsequent write cycles. When E (W) is Low, and

UB or LB is Low, write cycle begins on the W (E)’s

falling edge. Therefore, address setup time is

referenced to Write Enable as t

AVWL

and to Chip

Enable as t

AVEL

and is determined by the latter

occurring edge.

transitions

for

The Write cycle can be terminated by the earlier

rising edge of E or W.

If the Output is enabled (E = Low, G = Low, LB or

UB = Low), then W will return the outputs to high

impedance within t

WLQZ

of its falling edge. Care

must be taken to avoid bus contention in this type

of operation. Data input must be valid for t

DVWH

before the rising edge of Write Enable, or for t

DVEH

before the rising edge of E, whichever occurs first,

and remain valid for t

WHDX

and t

EHDX

respectively.

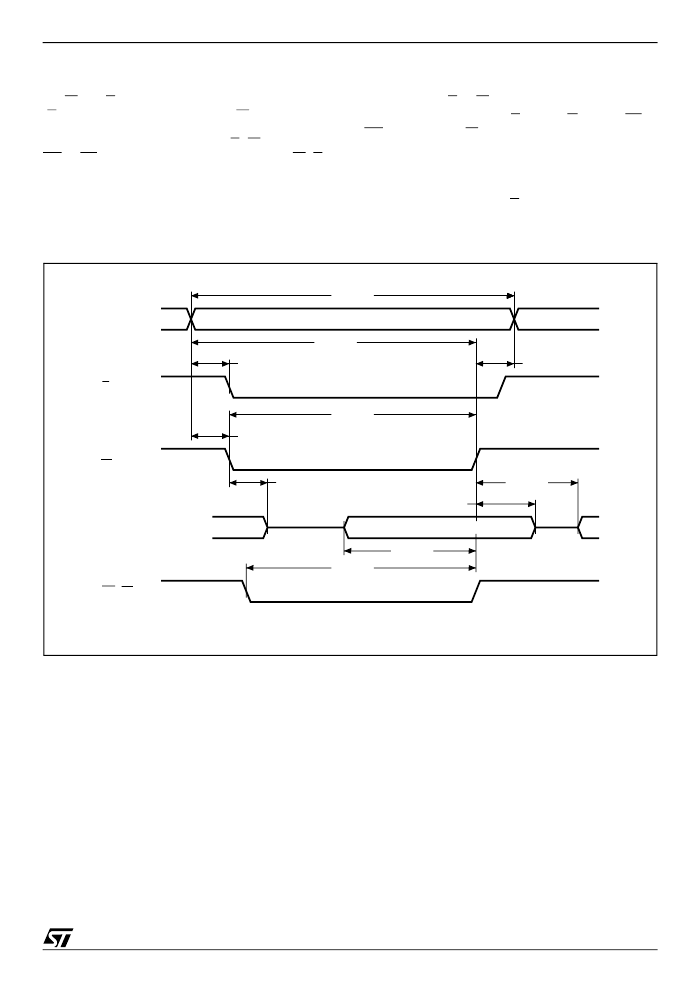

Figure 10. Write Enable Controlled, Write AC Waveforms

AI04878

tAVAV

tWHAX

tDVWH

DATA INPUT

A0-A15

E

W

DQ0-DQ15

VALID

tAVWH

tAVEL

tWLWH

tAVWL

tWLQZ

tWHDX

tWHQX

tBLWH

UB, LB

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M68AW127BM10MC1T | 1Mbit 128K x8, 3.0V Asynchronous SRAM |

| M68AW127BM10MC6T | 1Mbit 128K x8, 3.0V Asynchronous SRAM |

| M68AW127BM10N1T | 1Mbit 128K x8, 3.0V Asynchronous SRAM |

| M68AW127BM10N6T | 1Mbit 128K x8, 3.0V Asynchronous SRAM |

| M68AW127BM10NK6T | 1Mbit 128K x8, 3.0V Asynchronous SRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M68AW064FL55ZB6T | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:1 Mbit 64K x16 3.0V Asynchronous SRAM |

| M68AW064FL70ZB1 | 制造商:STMicroelectronics 功能描述: |

| M68AW064FL70ZB1T | 制造商:STMicroelectronics 功能描述: |

| M68AW064FL70ZB6T | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:1 Mbit 64K x16 3.0V Asynchronous SRAM |

| M68AW064FZB | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:1 Mbit 64K x16 3.0V Asynchronous SRAM |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。