- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377840 > M95128-MN6PP (意法半導(dǎo)體) 128 Kbit Serial SPI bus EEPROM with high speed clock PDF資料下載

參數(shù)資料

| 型號(hào): | M95128-MN6PP |

| 廠商: | 意法半導(dǎo)體 |

| 元件分類: | DRAM |

| 英文描述: | 128 Kbit Serial SPI bus EEPROM with high speed clock |

| 中文描述: | 128千位的SPI高速時(shí)鐘總線的EEPROM |

| 文件頁(yè)數(shù): | 23/41頁(yè) |

| 文件大小: | 207K |

| 代理商: | M95128-MN6PP |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)當(dāng)前第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)

M95128, M95128-W, M95128-R

Delivery state

23/41

6

Delivery state

The device is delivered with the memory array set at all 1s (FFh). The Status Register Write

Disable (SRWD) and Block Protect (BP1 and BP0) bits are initialized to 0.

7

Connecting to the SPI bus

These devices are fully compatible with the SPI protocol.

All instructions, addresses and input data bytes are shifted in to the device, most significant

bit first. The Serial Data Input (D) is sampled on the first rising edge of the Serial Clock (C)

after Chip Select (S) goes Low.

All output data bytes are shifted out of the device, most significant bit first. The Serial Data

Output (Q) is latched on the first falling edge of the Serial Clock (C) after the instruction

(such as the Read from Memory Array and Read Status Register instructions) have been

clocked into the device.

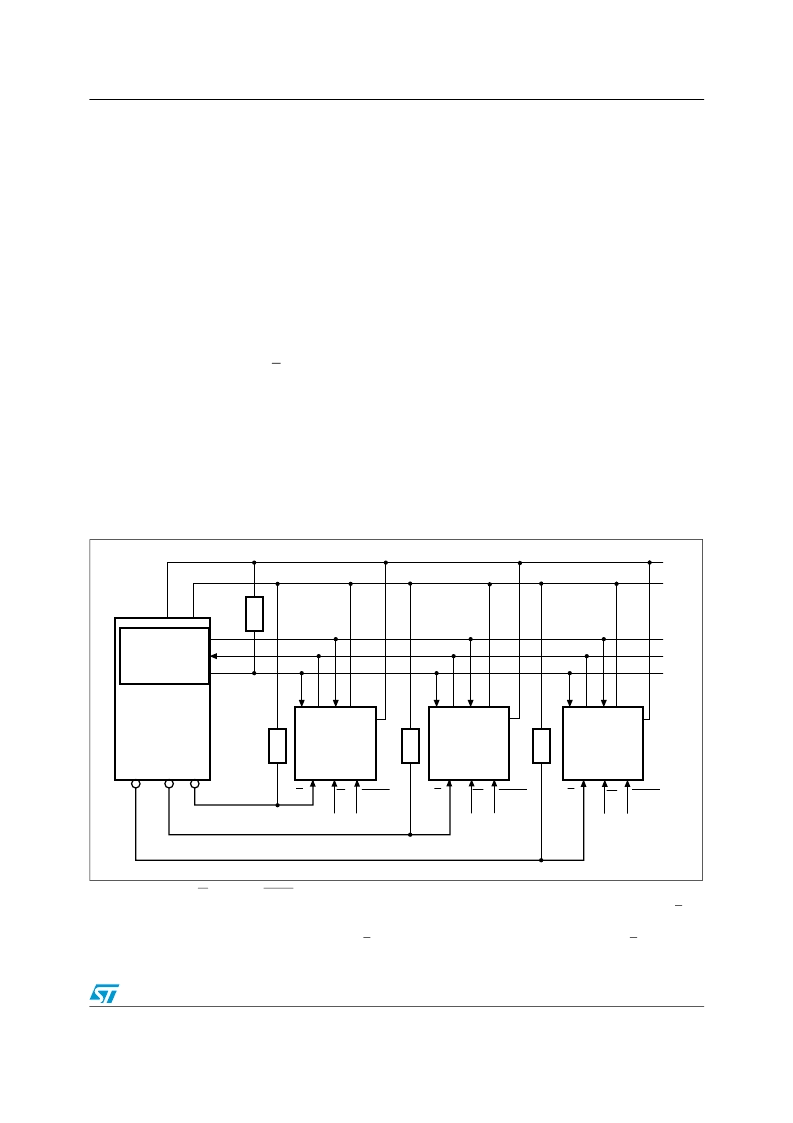

Figure 12

shows three devices, connected to an MCU, on a SPI bus. Only one device is

selected at a time, so only one device drives the Serial Data Output (Q) line at a time, all the

others being high impedance.

Figure 12.

Bus master and memory devices on the SPI bus

1.

2.

The Write Protect (W) and Hold (HOLD) signals should be driven, High or Low as appropriate.

These pull-up resistors, R, ensure that the M95128, M95128-W, M95128-R

are not selected if the Bus Master leaves the S

line in the high-impedance state. As the Bus Master may enter a state where all inputs/outputs are in high impedance at the

same time (that is when the Bus Master is reset), the clock line (C) must be connected to an external pull-down resistor so

that, when all inputs/outputs become high impedance, S is pulled High while C is pulled Low (thus ensuring that S and C do

not become High at the same time, and so, that the t

SHCH

requirement is met).

AI12304b

Bus Master

SPI Memory

Device

SDO

SDI

SCK

C

Q

D

S

SPI Memory

Device

C

Q

D

S

SPI Memory

Device

C

Q

D

S

CS3

CS2 CS1

SPI Interface with

(CPOL, CPHA) =

(0, 0) or (1, 1)

W

HOLD

W

HOLD

W

HOLD

R

(2)

R

(2)

R

(2)

V

CC

V

CC

V

CC

V

CC

V

SS

V

SS

V

SS

V

SS

R

(2)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M95128-MN6PV | 128 Kbit Serial SPI bus EEPROM with high speed clock |

| M95128-MN6TGP | 128 Kbit Serial SPI bus EEPROM with high speed clock |

| M95128-MN6TGV | 128 Kbit Serial SPI bus EEPROM with high speed clock |

| M95128-MN6TPP | 128 Kbit Serial SPI bus EEPROM with high speed clock |

| M95128-MN6TV | 128 Kbit Serial SPI bus EEPROM with high speed clock |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M95128-MN6PV | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:128 Kbit Serial SPI bus EEPROM with high speed clock |

| M95128-MN6T | 功能描述:電可擦除可編程只讀存儲(chǔ)器 5.5V 128K (16Kx8) RoHS:否 制造商:Atmel 存儲(chǔ)容量:2 Kbit 組織:256 B x 8 數(shù)據(jù)保留:100 yr 最大時(shí)鐘頻率:1000 KHz 最大工作電流:6 uA 工作電源電壓:1.7 V to 5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-8 |

| M95128-MN6TG | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:256Kbit and 128Kbit Serial SPI Bus EEPROM With High Speed Clock |

| M95128-MN6TG/A | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:128 Kbit serial SPI bus EEPROM with high speed clock |

| M95128-MN6TG/P | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:128 Kbit serial SPI bus EEPROM with high speed clock |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。