- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄9467 > MAX1046BETX+ (Maxim Integrated Products)IC ADC/DAC 10BIT 36-TQFN-EP PDF資料下載

參數(shù)資料

| 型號: | MAX1046BETX+ |

| 廠商: | Maxim Integrated Products |

| 文件頁數(shù): | 10/39頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC ADC/DAC 10BIT 36-TQFN-EP |

| 產(chǎn)品培訓(xùn)模塊: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 標(biāo)準(zhǔn)包裝: | 50 |

| 類型: | ADC,DAC |

| 分辨率(位): | 10 b |

| 采樣率(每秒): | 225k |

| 數(shù)據(jù)接口: | 串行 |

| 電壓電源: | 模擬和數(shù)字 |

| 電源電壓: | 4.75 V ~ 5.25 V |

| 工作溫度: | -40°C ~ 85°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 36-WFQFN 裸露焊盤 |

| 供應(yīng)商設(shè)備封裝: | 36-TQFN 裸露焊盤(6x6) |

| 包裝: | 管件 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁當(dāng)前第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁

MAX1040/MAX1042/MAX1046/MAX1048

10-Bit, Multichannel ADCs/DACs with FIFO,

Temperature Sensing, and GPIO Ports

18

______________________________________________________________________________________

Celsius (two’s complement), at a resolution of 8 LSB

per degree. See the

Temperature Measurements sec-

tion for details on converting the digital code to a tem-

perature.

10-Bit DAC

In addition to the 10-bit ADC, the MAX1040/MAX1042/

MAX1046/MAX1048 also include four voltage-output,

10-bit, monotonic DACs with less than 1 LSB integral

nonlinearity error and less than 0.5 LSB differential non-

linearity error. Each DAC has a 2s settling time and

ultra-low glitch energy (4nVs). The 10-bit DAC code is

unipolar binary with 1 LSB = VREF / 1024.

DAC Digital Interface

Figure 1 shows the functional diagram of the MAX1042.

The shift register converts a serial 16-bit word to parallel

data for each input register operating with a clock rate

up to 25MHz. The SPI-compatible digital interface to the

shift register consists of

CS, SCLK, DIN, and DOUT.

Serial data at DIN is loaded on the falling edge of SCLK.

Pull

CS low to begin a write sequence. Begin a write to

the DAC by writing 0001XXXX as a command byte. The

last 4 bits of the DAC select register are don’t-care bits.

See Table 10. Write another 2 bytes to the DAC inter-

face register following the command byte to select the

appropriate DAC and the data to be written to it. See

Tables 17 and 18.

The four double-buffered DACs include an input and a

DAC register. The input registers are directly connect-

ed to the shift register and hold the result of the most

recent write operation. The four 10-bit DAC registers

hold the current output code for the respective DAC.

Data can be transferred from the input registers to the

DAC registers by pulling

LDAC low or by writing the

appropriate DAC command sequence at DIN. See

Table 17. The outputs of the DACs are buffered through

four rail-to-rail op amps.

The MAX1040/MAX1042/MAX1046/MAX1048 DAC out-

put voltage range is based on the internal reference or

an external reference. Write to the setup register (see

Table 5) to program the reference. If using an external

voltage reference, bypass REF1 with a 0.1F capacitor

to AGND. The internal reference is 4.096V. When using

an external reference, the voltage range is 0.7V to AVDD.

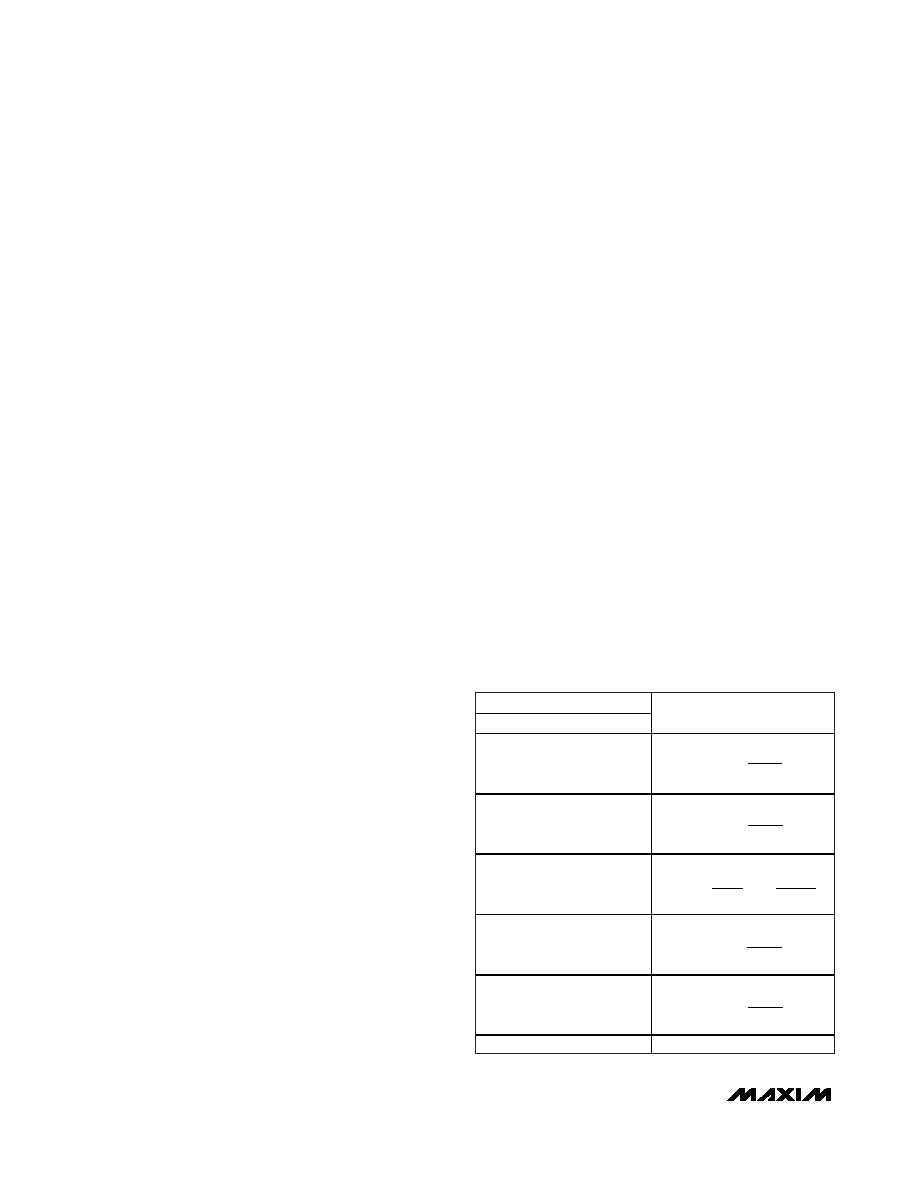

DAC Transfer Function

See Table 2 for various analog outputs from the DAC.

DAC Power-On Wake-Up Modes

The state of the RES_SEL input determines the wake-up

state of the DAC outputs. Connect RES_SEL to AVDD or

AGND upon power-up to be sure the DAC outputs

wake up to a known state. Connect RES_SEL to AGND

to wake up all DAC outputs at 000h. While RES_SEL is

low, the 100kΩ internal resistor pulls the DAC outputs to

AGND and the output buffers are powered down.

Connect RES_SEL to AVDD to wake up all DAC outputs

at FFFh. While RES_SEL is high, the 100kΩ pullup

resistor pulls the DAC outputs to VREF1 and the output

buffers are powered down.

DAC Power-Up Modes

See Table 18 for a description of the DAC power-up

and power-down modes.

GPIOs

In addition to the internal ADC and DAC, the

MAX1042/MAX1048 also provide four GPIO channels,

GPIOA0, GPIOA1, GPIOC0, and GPIOC1. Read and write

to the GPIOs as detailed in Table 1 and Tables 12–16.

Also, see the

GPIO Command section. See Figures 11 and

12 for GPIO timing.

DAC CONTENTS

MSB

LSB

ANALOG OUTPUT

11

1111

10

0000

0001

10

0000

01

0111

00

0000

0001

00

0000

0

+

VREF

1023

1024

+

=

+

V

REF

512

1024

2

+

VREF

511

1024

+

VREF

1

1024

+

VREF

1023

1024

Table 2. DAC Output Code Table

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MS27466T25B35PD | CONN RCPT 128POS WALL MNT W/PINS |

| VE-BVT-MY-S | CONVERTER MOD DC/DC 6.5V 50W |

| LTC6992IDCB-1#TRMPBF | IC OSC SILICON 1MHZ 6-DFN |

| LTC6908IDCB-2#TRMPBF | IC OSC SILICON 10MHZ 6-DFN |

| LTC6904CMS8#TRPBF | IC OSC SILICON 68MHZ 8-MSOP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MAX1046BETX+ | 功能描述:ADC / DAC多通道 10Bit AD/DACs w/FIFO Temp Sns & GPIO Port RoHS:否 制造商:Texas Instruments 轉(zhuǎn)換速率: 分辨率:8 bit 接口類型:SPI 電壓參考: 電源電壓-最大:3.6 V 電源電壓-最小:2 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-40 |

| MAX1046BETX+T | 功能描述:ADC / DAC多通道 10Bit AD/DACs w/FIFO Temp Sns & GPIO Port RoHS:否 制造商:Texas Instruments 轉(zhuǎn)換速率: 分辨率:8 bit 接口類型:SPI 電壓參考: 電源電壓-最大:3.6 V 電源電壓-最小:2 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-40 |

| MAX1046BETX-T | 功能描述:ADC / DAC多通道 RoHS:否 制造商:Texas Instruments 轉(zhuǎn)換速率: 分辨率:8 bit 接口類型:SPI 電壓參考: 電源電壓-最大:3.6 V 電源電壓-最小:2 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-40 |

| MAX1048 | 制造商:MAXIM 制造商全稱:Maxim Integrated Products 功能描述:10-Bit, Multichannel ADCs/DACs with FIFO, Temperature Sensing, and GPIO Ports |

| MAX1048BETX | 功能描述:ADC / DAC多通道 RoHS:否 制造商:Texas Instruments 轉(zhuǎn)換速率: 分辨率:8 bit 接口類型:SPI 電壓參考: 電源電壓-最大:3.6 V 電源電壓-最小:2 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-40 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。