- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄1936 > MAX14824GTG+ (Maxim Integrated Products)IC IO-LINK MASTER TXRX 24TQFN PDF資料下載

參數(shù)資料

| 型號: | MAX14824GTG+ |

| 廠商: | Maxim Integrated Products |

| 文件頁數(shù): | 7/28頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC IO-LINK MASTER TXRX 24TQFN |

| 標(biāo)準(zhǔn)包裝: | 75 |

| 系列: | * |

第1頁第2頁第3頁第4頁第5頁第6頁當(dāng)前第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁

15

MAX14824

IO-Link Master Transceiver

Pin Description (continued)

Detailed Description

The MAX14824 is an IO-LinkM master transceiver that

integrates an IO-Link physical interface with an additional

24V digital input and two LDOs. A 12MHz SPIK interface

allows fast programming and monitoring.

The device supports COM1, COM2, and COM3 IO-Link

data rates and has the option of limiting emitted EMI by

selecting a lower slew rate at lower data rates. The auto-

matic wake-up circuitry determines the correct wake-up

pulse polarity, allowing the use of simple UARTs for

wake-up pulse generation.

The C/Q and DI inputs have selectable current sinks that

can be enabled for use in actuators.

The device is configured and monitored through an SPI

interface. Extensive alarms are available through SPI.

24V Interface

The device features an IO-Link transceiver interface

capable of operating with voltages up to 36V. This

includes the C/Q input/output and the logic-level digital

input (DI).

DI is reverse-polarity protected. Short-circuit protection is

provided on the C/Q driver.

Configurable C/Q Driver

The device’s C/Q driver has a selectable push-pull, high-

side (PNP), or low-side (NPN) switching driver.

Set the C/Q_N/P and C/Q_PP bits in the CQConfig reg-

ister to select the driver mode for the C/Q driver. When

configured as a push-pull output, C/Q switches between

VCC and ground. Set the C/Q_PP bit to 1 to select push-

pull operation. Set the C/Q_PP bit to 0 to configure the

C/Q output for open-drain operation. The C/Q_N/P bit

selects NPN or PNP operation when C/Q is configured as

an open-drain output.

C/Q Driver and Receiver

The C/Q driver can be enabled through hardware

(TXEN) or software (C/QDEn). Drive TXEN high to

enable the C/Q driver and drive TXEN low to disable

the driver. The C/Q driver can be enabled through the

C/QDEn bit in the C/QConfig register.

The C/Q driver on the device is specified for 300mA

to drive large capacitive loads over 1FF and dynamic

impedances like incandescent lamps.

IO-Link is a registered trademark of Procibus User

Organization (PNO).

SPI is a trademark of Motorola Inc.

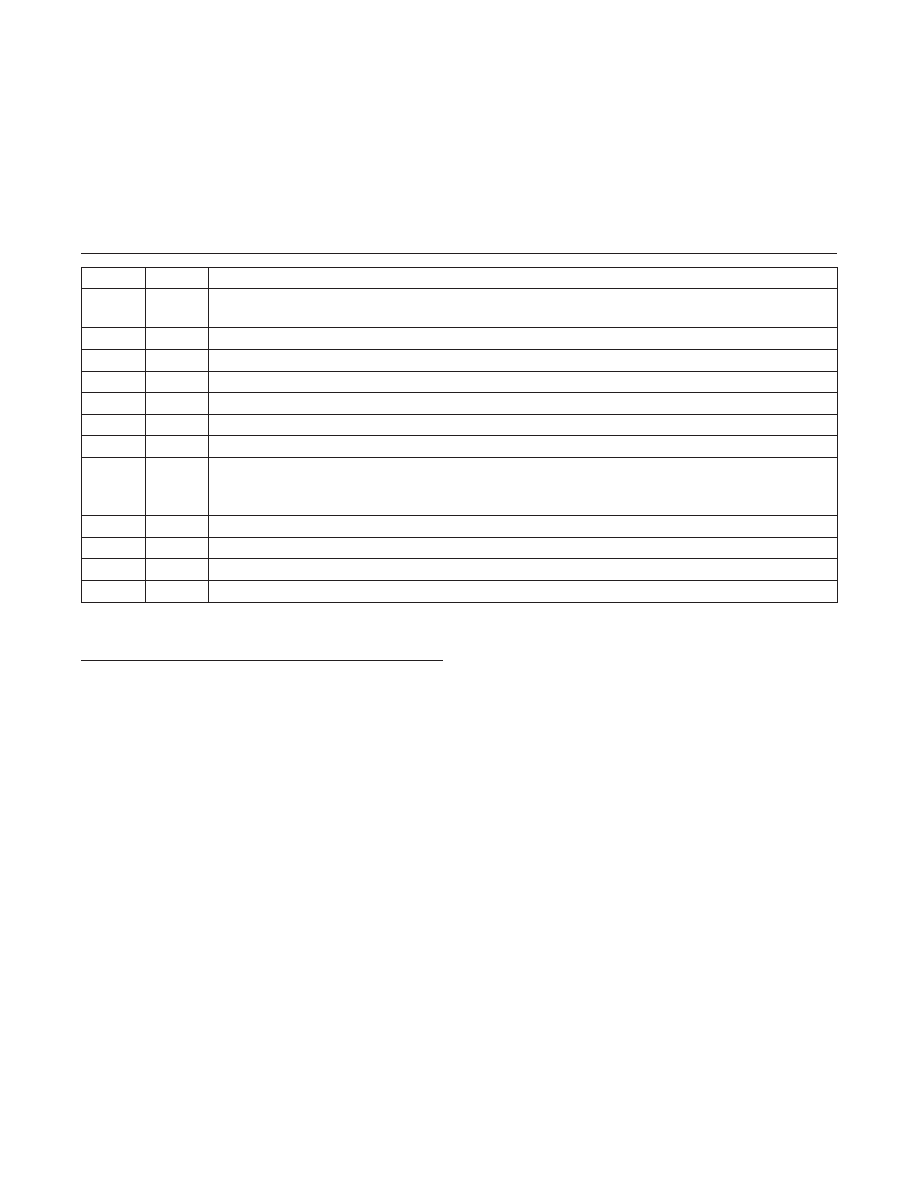

PIN

NAME

FUNCTION

14

RX

Receiver Output. RX is the inverse logic level of C/Q. RX is always high when the RxDis bit in the

CQConfig register is set to 1.

15

WUEN

Wake-Up Enable Input. Drive WUEN high to enable automatic wake-up pulse generation.

16

A2

Chip-Select Address Input 2. Do not leave A2 unconnected.

17

LI

Logic Output of 24V DI Logic Input. LI is the inverse logic of DI. LI is referenced to VL.

18

UV

Open-Drain Undervoltage Indicator Output. UV is active high.

19

DI

24V Logic-Level Digital Input

20

GND

Ground

21

C/Q

SIO/IO-Link Data Input/Output. Drive TXEN high to enable the C/Q driver. The logic on the C/Q output is

the inverse logic level of the signals on the TXC and TXQ inputs. Drive TXEN low to disable the C/Q

driver. RX is the logic inverse of C/Q.

22

A1

Chip-Select Address Input 1. Do not leave A1 unconnected.

23

VCC

Power-Supply Input. Bypass VCC to GND with a 1FF ceramic capacitor.

24

A0

Chip-Select Address Input 0. Do not leave A0 unconnected.

—

EP

Exposed Pad. Connect EP to GND.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MAX1482CSD-T | IC TXRX RS485/422 250KBPS 14SOIC |

| MAX14830ETM+ | SEMICONDUCTOR OTHER |

| MAX14841EASA+T | IC TXRX RS485 40MBPS 8SOIC |

| MAX1484CUB+ | IC TXRX RS485/RS422 10-UMAX |

| MAX1488EESD | IC DVR RS232 QUAD 120KBPS 14SOIC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MAX14824GTG+ | 功能描述:輸入/輸出控制器接口集成電路 3 1/2 Digit ADC w/Reference RoHS:否 制造商:Silicon Labs 產(chǎn)品: 輸入/輸出端數(shù)量: 工作電源電壓: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:QFN-64 封裝:Tray |

| MAX14824GTG+T | 功能描述:輸入/輸出控制器接口集成電路 Logic-Level Translator RoHS:否 制造商:Silicon Labs 產(chǎn)品: 輸入/輸出端數(shù)量: 工作電源電壓: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:QFN-64 封裝:Tray |

| MAX14825ETG+ | 功能描述:輸入/輸出控制器接口集成電路 Master IO-Link Schneider RoHS:否 制造商:Silicon Labs 產(chǎn)品: 輸入/輸出端數(shù)量: 工作電源電壓: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:QFN-64 封裝:Tray |

| MAX14825ETG+T | 功能描述:輸入/輸出控制器接口集成電路 NULL RoHS:否 制造商:Silicon Labs 產(chǎn)品: 輸入/輸出端數(shù)量: 工作電源電壓: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:QFN-64 封裝:Tray |

| MAX1482C/D DIE | 制造商:Maxim Integrated Products 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。