- 您現(xiàn)在的位置:買賣IC網 > PDF目錄2158 > MAX5166NECM+T (Maxim Integrated Products)IC AMP SAMPLE/HOLD 32CH 48-LQFP PDF資料下載

參數(shù)資料

| 型號: | MAX5166NECM+T |

| 廠商: | Maxim Integrated Products |

| 文件頁數(shù): | 10/12頁 |

| 文件大小: | 0K |

| 描述: | IC AMP SAMPLE/HOLD 32CH 48-LQFP |

| 產品培訓模塊: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 標準包裝: | 2,000 |

| 放大器類型: | 采樣和保持 |

| 電路數(shù): | 32 |

| 電流 - 輸入偏壓: | 1µA |

| 電壓 - 輸入偏移: | 5000µV |

| 電流 - 電源: | 36mA |

| 電流 - 輸出 / 通道: | 2mA |

| 工作溫度: | -40°C ~ 85°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 48-LQFP |

| 供應商設備封裝: | 48-LQFP(7x7) |

| 包裝: | 帶卷 (TR) |

Hold Step

When switching between sample mode and hold

mode, the voltage of the hold capacitor changes due to

charge injection from stray capacitance. This voltage

change, called hold step, is minimized by limiting the

amount of stray capacitance seen by the hold capaci-

tor. The MAX5166 limits the hold step to 0.25mV (typ).

An output capacitor to ground can be used to filter out

this small hold-step error.

Output

The MAX5166 contains an output buffer for each multi-

plexer channel (32 total), so the hold capacitor sees a

high-impedance input, reducing the droop rate. While

in hold mode, the hold capacitor discharges at a rate of

1mV/sec (typ). The buffer also provides a low output

impedance; however, the device contains output resis-

tors in series with the buffer output (Figure 1) for select-

ed output filtering. To provide greater design flexibility,

the MAX5166 is available with an RO of 50

, 500, or

1k

.

Note: Output loads increase the analog supply cur-

rent (IDD and ISS). Excessive loading of the output(s)

damages the device by consuming more power than

the device will dissipate (see Absolute Maximum

Ratings). The resistor-divider formed by the output

resistor (ROUT_) and load impedance (RL) scales the

sampled voltage (VSAMP). Determine the output volt-

age (VOUT_) as follows:

Voltage Gain = AV = RL/(RL + ROUT)

VOUT_ = VSAMP AV

The maximum output voltage range depends on the

analog supply voltages available and the scaling factor

used:

(VSS + 0.75V) AV

≤ VOUT_ ≤ (VDD - 2.4V) AV

when RL =

∞, then AV = 1, and this equation becomes

(VSS + 0.75V)

≤ VOUT ≤ (VDD - 2.4V).

Timing Definitions

Acquisition time (tAQ) is the amount of time the

MAX5166 must remain in sample mode for the hold

capacitor to acquire an accurate sample. The hold-

mode settling time (tH) is the amount of time necessary

for the output voltage to settle to its final value.

Aperture delay (tAP) is the time interval required to dis-

connect the input from the hold capacitor. The inhibit

pulse width (tPW) is the amount of time the MAX5166

must remain in hold mode while the address is

changed. The data setup time (tDS) is the amount of

time an address must be maintained before the

address becomes valid. The data hold time (tDH) is the

amount of time an address must be maintained after

mode select has gone from low to high (Figure 2).

MAX5166

32-Channel Sample/Hold Amplifier

with Four Multiplexed Inputs

_______________________________________________________________________________________

7

0

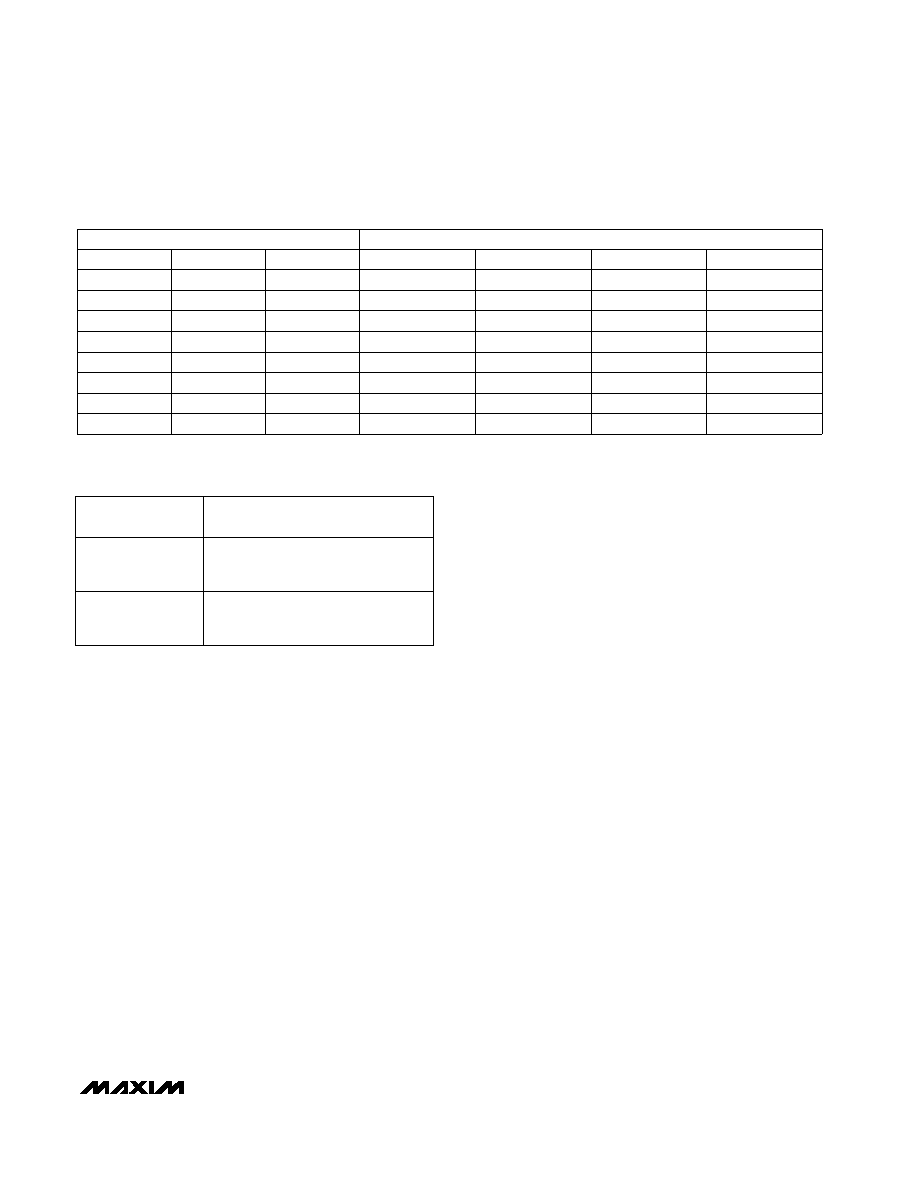

Table 1. Output Selection

Table 2. Mode Selection

0

1

0

1

0

1

ADDRESS

0

1

0

1

OUT2

OUT3

OUT6

OUT0

OUT7

OUT1

OUT4

OUT5

OUT10

OUT11

OUT14

OUT8

OUT15

OUT9

OUT12

OUT13

OUT18

OUT19

OUT22

OUT16

OUT23

OUT17

OUT20

OUT21

OUTPUT SELECTED

OUT26

OUT27

OUT30

OUT24

OUT31

OUT25

OUT28

OUT29

A2

A1

A0

MUX0

MUX1

MUX2

MUX3

0 = Logic Low, 1 = Logic High

0

1

Sample mode enabled on selected

analog multiplexer and channel

(Table 1).

Hold mode enabled on selected

analog multiplexer and channel

(Table 1).

MODE-SELECT

INPUTS* (M3–M0)

ACTION

0 = Logic Low, 1 = Logic High

* Only one M_ input asserted low; all others must be logic high

to meet the timing specification (see Single vs. Simultaneous

Sampling).

相關PDF資料 |

PDF描述 |

|---|---|

| MAX5167MCCM+T | IC AMP SAMPLE/HOLD 32CH 48-LQFP |

| MAX5168NCCM+T | IC AMP SAMPLE/HOLD 32CH 48-LQFP |

| MAX9610FELT+T | IC AMP CURR SENSE 50V/V 6UDFN |

| MAX9611AUB+T | IC 12BIT ADC OPAMP COMPAR 10UMAX |

| MAX9614AXT+T | IC OPAMP GP RR 2.8MHZ LP SC70-6 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| MAX5167 | 制造商:MAXIM 制造商全稱:Maxim Integrated Products 功能描述:32-Channel Sample/Hold Amplifier with Output Clamping Diodes |

| MAX5167LCCM | 功能描述:采樣&保持放大器 RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 捕獲時間:20 us 電源電壓-最大:18 V 最大工作溫度:+ 85 C 最小工作溫度:- 25 C 安裝風格: 封裝 / 箱體:SOIC-14 封裝:Tube |

| MAX5167LCCM+ | 功能描述:采樣&保持放大器 32Ch Sample/Hold Amp RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 捕獲時間:20 us 電源電壓-最大:18 V 最大工作溫度:+ 85 C 最小工作溫度:- 25 C 安裝風格: 封裝 / 箱體:SOIC-14 封裝:Tube |

| MAX5167LCCM+T | 功能描述:采樣&保持放大器 32Ch Sample/Hold Amp RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 捕獲時間:20 us 電源電壓-最大:18 V 最大工作溫度:+ 85 C 最小工作溫度:- 25 C 安裝風格: 封裝 / 箱體:SOIC-14 封裝:Tube |

| MAX5167LCCM-T | 功能描述:采樣&保持放大器 RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 捕獲時間:20 us 電源電壓-最大:18 V 最大工作溫度:+ 85 C 最小工作溫度:- 25 C 安裝風格: 封裝 / 箱體:SOIC-14 封裝:Tube |

發(fā)布緊急采購,3分鐘左右您將得到回復。