- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385550 > MAX781 (Maxim Integrated Products, Inc.) PDA/Hand-Held Computer Power Controller PDF資料下載

參數(shù)資料

| 型號: | MAX781 |

| 廠商: | Maxim Integrated Products, Inc. |

| 英文描述: | PDA/Hand-Held Computer Power Controller |

| 中文描述: | PDA手持計算機電源控制器 |

| 文件頁數(shù): | 15/24頁 |

| 文件大小: | 185K |

| 代理商: | MAX781 |

M

PDA/Hand-Held Computer Power Controller

______________________________________________________________________________________

15

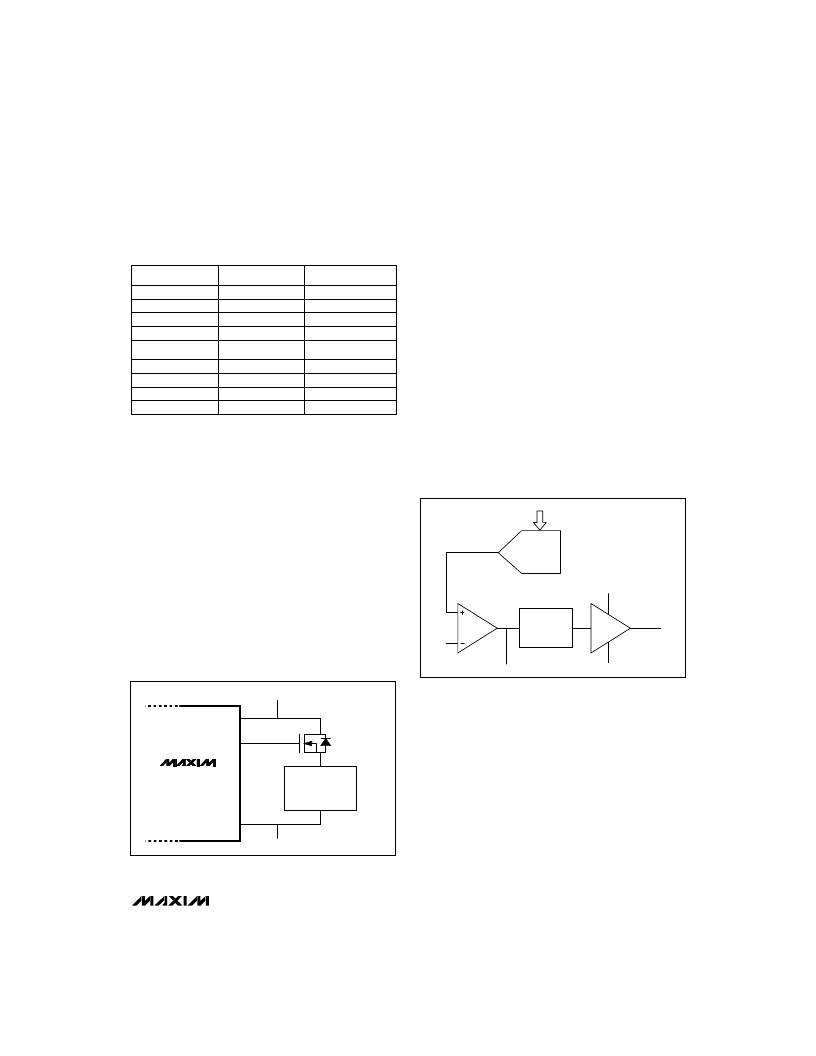

Gate Drivers

GD1 through GD5 are gate-driver outputs that high-

side drive external N-channel power MOSFETs. Loads

connected to 3OUT can be connected or disconnected

by using the circuitry shown in Figure 7. Clearing

GDSEL1 (GDSEL1 = 0) causes GD1 to sink up to

450μA to AGND. Setting GDSEL1 (GDSEL = 1) causes

GD1 to source up to 10μA from VHI. GD2–GD5 oper-

ate the same way. VHI is active (i.e., regulated to at

least 12.8V) only in operate mode, so the gate drivers

also only function in operate mode. GDSEL1 defaults

to a 1 on power-up. GDSEL2 through GDSEL5 default

to 0 on power-up.

FAST is a general-purpose output pin that sinks current

when FASTON = 1 and goes open drain when FASTON

= 0. FAST can be pulled up to any voltage up to 19V.

To use FAST as a general-purpose 3.3V logic output,

pull it up to 3OUT with a 100k

resistor. FAST may be

used to pull the gate of M3 down to connect the battery

to the input supply. The MAX781 does not limit the bat-

tery current when FAST is used in this way.

Battery Charger

The battery charger is a voltage-mode average current

regulator. Figure 8 shows a functional diagram of the

battery charger circuitry. The GMAMP is a transcon-

ductance amplifer with approximately 62dB of open-

loop DC gain. Set the GMAMP bandwidth with the

capacitor on COMP.

GMAMP bandwidth in hertz = gm / C

where gm = 0.0006 mho (mho = 1/

) and C = capaci-

tance on COMP in farads.

Average the current-sense signal by setting the

GMAMP bandwidth much lower than the battery-charg-

er switching frequency. The voltage output of the

GMAMP at COMP is converted to a duty cycle, which is

driven out of DCHG.

Serial-configuration bits CHG6–CHG0 set the average

current level. When CHG6–CHG0 are all set (1111111),

CSBAT is regulated to an average of 200mV. When

CHG6–CHG0 equals binary 0111111, CSBAT is regulat-

ed to an average of 100mV.

Analog Multiplexer

The MAX781’s built-in buffered analog multiplexer

selects one of eight different signal sources to be out-

put from the AOUT pin. Figure 9 shows the analog mul-

tiplexer circuitry. The AOUT buffer amplifier is disabled

in the shutdown and low-power modes, leaving the

89.7k

resistor to pull AOUT down to ground. Program

the MUX0, MUX1, MUX2 bits in the serial-configuration

data to select the analog multiplexer channel (Table 6).

Resistive dividers in the signal paths scale the chan-

nels to ensure that AOUT is scaled to REF. The AOUT

buffer amplifier can sink or source 1mA.

VPPA0

1

1

0

0

1

1

0

1

0

1

0

1

0

VPPA1

1

0

0

VPPB1

VPPB0

VPPA Voltage (V)

0

5

12

3.3

5

12

3.3

0

VPPB Voltage (V)

Table 5. VPPA and VPPB Control Bits

MAX781

3.3V LOAD THAT

NEEDS TOBE TURNED

ON/OFF

GD_

3OUT

N-CHANNEL

POWER MOSFET

...TOREST OF 3OUT CIRCUIT

...TOREST OF AGND CONNECTIONS

AGND

Figure 7. Using the Gate Drivers for High-Side Load Switching

GMAMP

DCHG

DCHG = 5OUT

EXTERNAL SWITCH OFF

DCHG = AGND

EXTERNAL SWITCH ON

PGND

5OUT

AT 0% DUTY CYCLE

,

DCHG = 5OUT

COMP

VOLTAGE TO

DUTY CYCLE

CONVERTER

7-BIT DAC

CHG6–CHG0

CSBAT

DACOUT

(0mV TO200mV)

Figure 8. Battery-Charger Block Diagram

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MAX781CBX | PDA/Hand-Held Computer Power Controller |

| MAX781EBX | PDA/Hand-Held Computer Power Controller |

| MAX783 | Triple-Output Power-Supply Controller for Notebook Computers(3.3V/5V,具有雙組PCMCIA標(biāo)準(zhǔn)VPP輸出的筆記本電腦電源控制器) |

| MAX786 | Dual-Output Power-Supply Controller for Notebook Computers(具有25μA關(guān)斷的,3.3V/5V筆記本型電腦電源) |

| MAX787 | 5V/3.3V/3V 5A Step-Down, PWM, Switch-Mode DC-DC Regulators(5A,5V步降,PWM,開關(guān)型DC-DC變換器) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MAX781CBX | 制造商:Maxim Integrated Products 功能描述: |

| MAX7828BQ | 制造商:Maxim Integrated Products 功能描述:NON BOOK, REQUIRES NCNR, Q# - Rail/Tube |

| MAX7828UQ/883B | 制造商:Maxim Integrated Products 功能描述:NON BOOK, REQUIRES NCNR, Q# - Rail/Tube |

| MAX782C/D | 功能描述:DC/DC 開關(guān)控制器 Triple-Output Power-Supply Controller for Notebook Computers RoHS:否 制造商:Texas Instruments 輸入電壓:6 V to 100 V 開關(guān)頻率: 輸出電壓:1.215 V to 80 V 輸出電流:3.5 A 輸出端數(shù)量:1 最大工作溫度:+ 125 C 安裝風(fēng)格: 封裝 / 箱體:CPAK |

| MAX782C/D+ | 功能描述:DC/DC 開關(guān)控制器 RoHS:否 制造商:Texas Instruments 輸入電壓:6 V to 100 V 開關(guān)頻率: 輸出電壓:1.215 V to 80 V 輸出電流:3.5 A 輸出端數(shù)量:1 最大工作溫度:+ 125 C 安裝風(fēng)格: 封裝 / 箱體:CPAK |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。