- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄1946 > MAX9205EAI/V+T (Maxim Integrated Products)IC SERIALIZER 10BIT LVDS 28SSOP PDF資料下載

參數(shù)資料

| 型號(hào): | MAX9205EAI/V+T |

| 廠商: | Maxim Integrated Products |

| 文件頁數(shù): | 11/13頁 |

| 文件大小: | 0K |

| 描述: | IC SERIALIZER 10BIT LVDS 28SSOP |

| 其它有關(guān)文件: | Automotive Product Guide |

| 產(chǎn)品培訓(xùn)模塊: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 標(biāo)準(zhǔn)包裝: | 2,000 |

| 功能: | 串行器 |

| 數(shù)據(jù)速率: | 400Mbps |

| 輸入類型: | LVTTL/LVCMOS |

| 輸出類型: | LVDS |

| 輸入數(shù): | 10 |

| 輸出數(shù): | 1 |

| 電源電壓: | 3 V ~ 3.6 V |

| 工作溫度: | -40°C ~ 85°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 28-SSOP(0.209",5.30mm 寬) |

| 供應(yīng)商設(shè)備封裝: | 28-SSOP |

| 包裝: | 帶卷 (TR) |

MAX9205/MAX9207

10-Bit Bus LVDS Serializers

7

Maxim Integrated

Applications Information

Power-Supply Bypassing

Bypass AVCC with high-frequency surface-mount

ceramic 0.1F and 0.001F capacitors in parallel as

close to the device as possible, with the smaller valued

capacitor closest to AVCC. Bypass DVCC with high-fre-

quency surface-mount ceramic 0.1F and 0.001F

capacitors in parallel as close to the device as possi-

ble, with the smaller valued capacitor closest to DVCC.

Differential Traces and Termination

Output trace characteristics affect the performance of

the MAX9205/MAX9207. Use controlled-impedance

media and terminate at both ends of the transmission

line in the media's characteristic impedance.

Termination with a single resistor at the end of a point-

to-point link typically provides acceptable performance.

However, the MAX9205/MAX9207 output levels are

specified for double-terminated point-to-point and mul-

tipoint applications. With a single 100

termination, the

output swing is larger.

Avoid the use of unbalanced cables such as ribbon or

simple coaxial cable. Balanced cables such as twisted

pair offer superior signal quality and tend to generate

less EMI due to canceling effects. Balanced cables

tend to pick up noise as common mode, which is

rejected by a differential receiver.

Eliminate reflections and ensure that noise couples as

common mode by running the differential traces close

together. Reduce skew by matching the electrical

length of the traces. Excessive skew can result in a

degradation of magnetic field cancellation.

The differential output signals should be routed close to

each other to cancel their external magnetic field.

Maintain a constant distance between the differential

traces to avoid discontinuities in differential impedance.

Avoid 90° turns and minimize the number of vias to fur-

ther prevent impedance discontinuities.

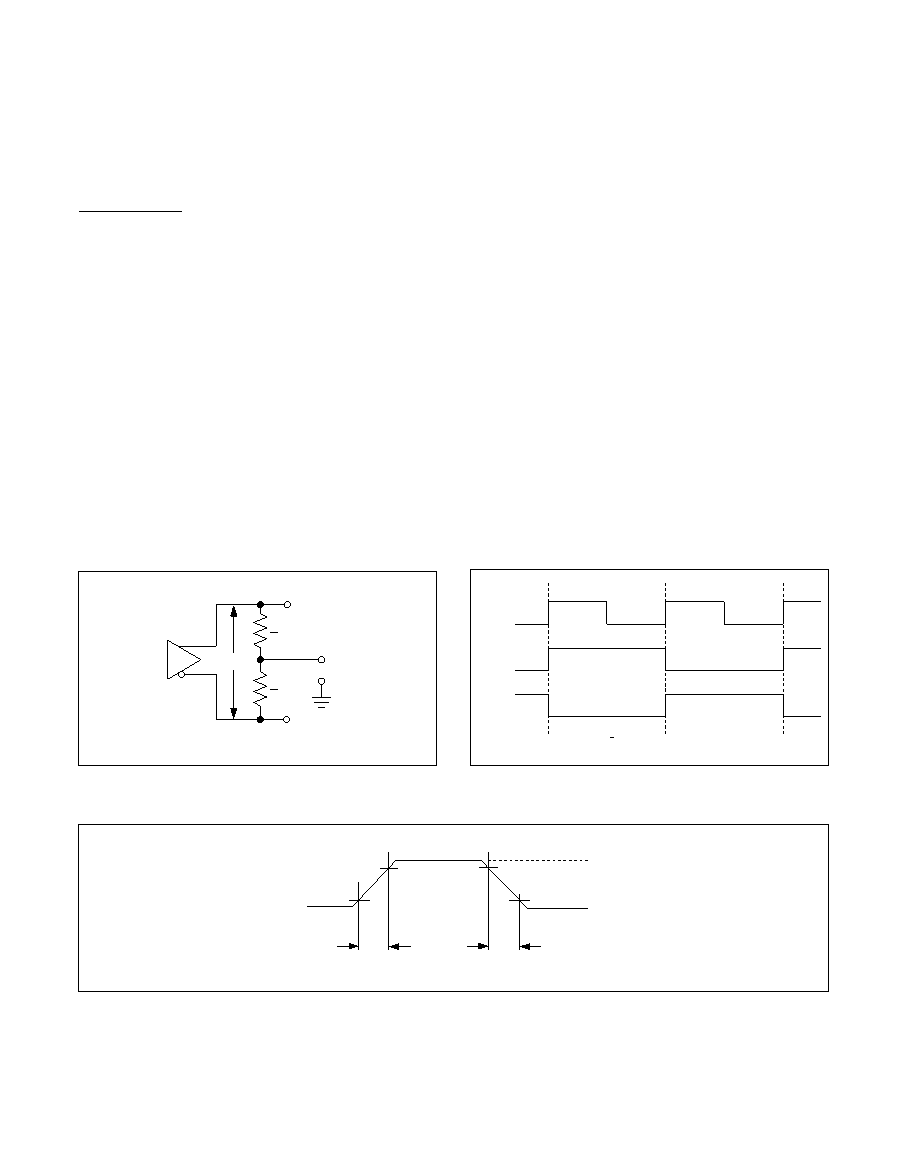

OUT+

OUT-

VOD

VOS

RL

2

RL

2

Figure 1. Output Voltage Definitions

TCLK

ODD IN_

EVEN IN_

TCLK_R/F = LOW

Figure 2. Worst-Case ICC Test Pattern

TCLK

tCLKT

10%

90%

10%

tCLKT

0

3V

Figure 3. Input Clock Transition Time Requirement

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MAX9208EAI+ | IC DESERIALIZER LVDS 28-SSOP |

| MAX9209GUM+D | IC PROG DC-BAL 21BIT SER 48TSSOP |

| MAX9213EUM+ | IC SERIALIZER PROG 48-TSSOP |

| MAX9214EUM+TD | IC DESERIALIZER PROG 48TSSOP |

| MAX9217ECM/V+ | IC SERIALIZER LVDS 48LQFP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MAX9205EAV | 制造商:MAXIM 制造商全稱:Maxim Integrated Products 功能描述:10-Bit Bus LVDS Serializers |

| MAX9205EVKIT | 制造商:Maxim Integrated Products 功能描述:10-BIT BUS LVDS SERIALIZER - Bulk |

| MAX9206 | 制造商:MAXIM 制造商全稱:Maxim Integrated Products 功能描述:10-Bit Bus LVDS Deserializers |

| MAX9206_07 | 制造商:MAXIM 制造商全稱:Maxim Integrated Products 功能描述:10-Bit Bus LVDS Deserializers |

| MAX9206_10 | 制造商:MAXIM 制造商全稱:Maxim Integrated Products 功能描述:10-Bit Bus LVDS Deserializers |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。