- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383540 > MAX9216EUM (MAXIM INTEGRATED PRODUCTS INC) Programmable DC-Balance 21-Bit Deserializers PDF資料下載

參數(shù)資料

| 型號(hào): | MAX9216EUM |

| 廠商: | MAXIM INTEGRATED PRODUCTS INC |

| 元件分類: | 通用總線功能 |

| 英文描述: | Programmable DC-Balance 21-Bit Deserializers |

| 中文描述: | QUAD LINE RECEIVER, PDSO48 |

| 封裝: | 6.10 MM, MO-153ED, TSSOP-48 |

| 文件頁(yè)數(shù): | 10/18頁(yè) |

| 文件大小: | 904K |

| 代理商: | MAX9216EUM |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)當(dāng)前第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)

M

Programmable DC-Balance

21-Bit Deserializers

10

______________________________________________________________________________________

AC-Coupling Benefits

Bit errors experienced with DC-coupling can be elimi-

nated by increasing the receiver common-mode voltage

range by AC-coupling. AC-coupling increases the com-

mon-mode voltage range of an LVDS receiver to nearly

the voltage rating of the capacitor. The typical LVDS dri-

ver output is 350mV centered on an offset voltage of

1.25V, making single-ended output voltages of 1.425V

and 1.075V. An LVDS receiver accepts signals from 0 to

2.4V, allowing approximately

±

1V common-mode differ-

ence between the driver and receiver on a DC-coupled

link (2.4V - 1.425V = 0.975V and 1.075V - 0V = 1.075V).

Common-mode voltage differences may be due to

ground potential variation or common-mode noise. If

there is more than

±

1V of difference, the receiver is not

guaranteed to read the input signal correctly and may

cause bit errors. AC-coupling filters low-frequency

ground shifts and common-mode noise and passes

high-frequency data. A common-mode voltage differ-

ence up to the voltage rating of the coupling capacitor

(minus half the differential swing) is tolerated. DC-bal-

anced coding of the data is required to maintain the dif-

ferential signal amplitude and limit jitter on an

AC-coupled link. A capacitor in series with each output

of the LVDS driver is sufficient for AC-coupling.

However, two capacitors—one at the serializer output

and one at the deserializer input—provide protection in

case either end of the cable is shorted to a high voltage.

Applications Information

Selection of AC-Coupling Capacitors

Voltage droop and the DSV of transmitted symbols

cause signal transitions to start from different voltage

levels. Because the transition time is finite, starting the

signal transition from different voltage levels causes

timing jitter. The time constant for an AC-coupled link

needs to be chosen to reduce droop and jitter to an

acceptable level.

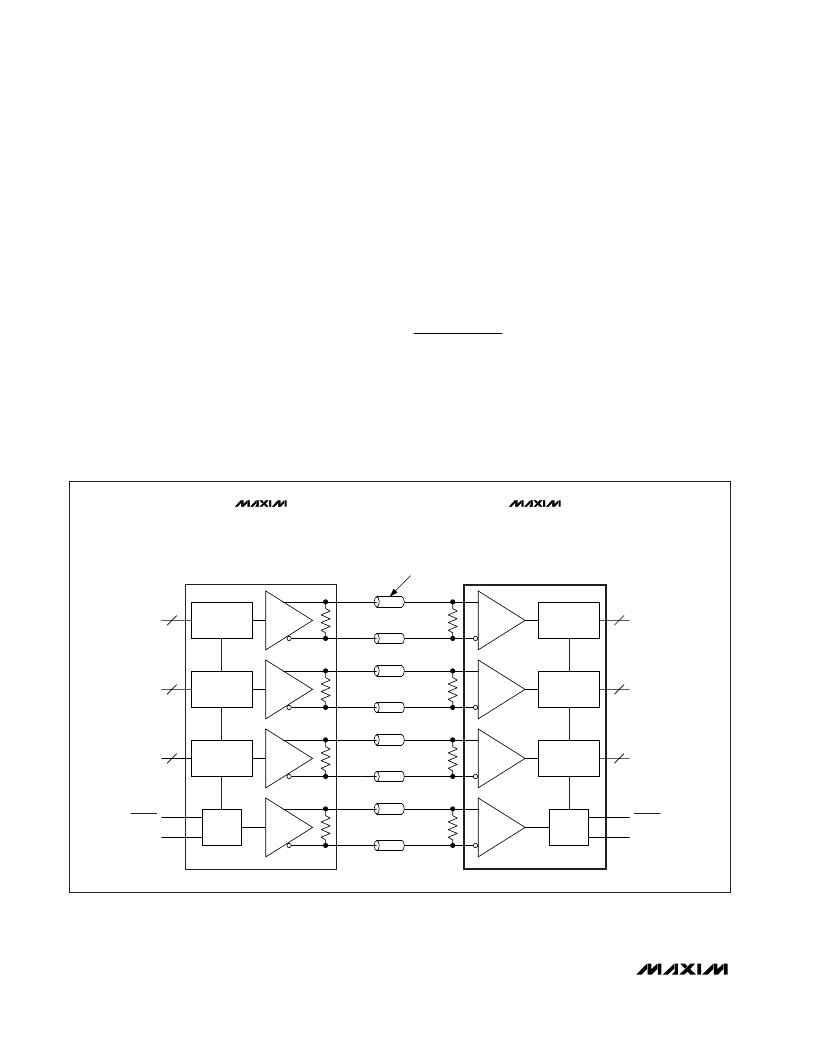

7 : 1

1 : 7

7

7

100

7 : 1

1 : 7

7

7

100

7 : 1

1 : 7

7

7

100

PLL

PLL

100

MAX9209

MAX9211

MAX9213

MAX9215

MAX9210

MAX9212

MAX9214

MAX9216

MAX9220

MAX9222

TxOUT

TxCLK OUT

RxIN

RxCLK IN

21:3 SERIALIZER

3:21 DESERIALIZER

PWRDWN

RxCLK OUT

RxOUT

PWRDWN

TxCLK IN

TxIN

TRANSMISSION LINE

Figure 11. DC-Coupled Link, Non-DC-Balanced Mode

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MAX9220EUM | Programmable DC-Balance 21-Bit Deserializers |

| MAX9222EUM | Programmable DC-Balance 21-Bit Deserializers |

| MAX9212ETM | Programmable DC-Balance 21-Bit Deserializers |

| MAX9214ETM | Programmable DC-Balance 21-Bit Deserializers |

| MAX9220ETM | Programmable DC-Balance 21-Bit Deserializers |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MAX9217 | 制造商:MAXIM 制造商全稱:Maxim Integrated Products 功能描述:27-Bit, 3MHz-to-35MHz DC-Balanced LVDS Serializer |

| MAX9217ECM | 功能描述:串行器/解串器 - Serdes 27-Bit DC-Balanced Serializer RoHS:否 制造商:Texas Instruments 類型:Deserializer 數(shù)據(jù)速率:1.485 Gbit/s 輸入類型:ECL/LVDS 輸出類型:LVCMOS 輸入端數(shù)量:1 輸出端數(shù)量:20 工作電源電壓:2.375 V to 2.625 V 工作溫度范圍:0 C to + 70 C 封裝 / 箱體:TQFP-64 |

| MAX9217ECM/V+ | 功能描述:串行器/解串器 - Serdes 27-Bit DC-Balanced Serializer RoHS:否 制造商:Texas Instruments 類型:Deserializer 數(shù)據(jù)速率:1.485 Gbit/s 輸入類型:ECL/LVDS 輸出類型:LVCMOS 輸入端數(shù)量:1 輸出端數(shù)量:20 工作電源電壓:2.375 V to 2.625 V 工作溫度范圍:0 C to + 70 C 封裝 / 箱體:TQFP-64 |

| MAX9217ECM/V+T | 功能描述:串行器/解串器 - Serdes 27-Bit DC-Balanced Serializer RoHS:否 制造商:Texas Instruments 類型:Deserializer 數(shù)據(jù)速率:1.485 Gbit/s 輸入類型:ECL/LVDS 輸出類型:LVCMOS 輸入端數(shù)量:1 輸出端數(shù)量:20 工作電源電壓:2.375 V to 2.625 V 工作溫度范圍:0 C to + 70 C 封裝 / 箱體:TQFP-64 |

| MAX9217ECM+ | 功能描述:串行器/解串器 - Serdes 27-Bit DC-Balanced Serializer RoHS:否 制造商:Texas Instruments 類型:Deserializer 數(shù)據(jù)速率:1.485 Gbit/s 輸入類型:ECL/LVDS 輸出類型:LVCMOS 輸入端數(shù)量:1 輸出端數(shù)量:20 工作電源電壓:2.375 V to 2.625 V 工作溫度范圍:0 C to + 70 C 封裝 / 箱體:TQFP-64 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。