- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄16169 > MAX9218EVKIT+ (Maxim Integrated Products)KIT PCB EVALUATION FOR MAX9218 PDF資料下載

參數(shù)資料

| 型號: | MAX9218EVKIT+ |

| 廠商: | Maxim Integrated Products |

| 文件頁數(shù): | 12/15頁 |

| 文件大?。?/td> | 0K |

| 描述: | KIT PCB EVALUATION FOR MAX9218 |

| 產(chǎn)品培訓模塊: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 標準包裝: | 1 |

| 系列: | * |

MAX9218

27-Bit, 3MHz-to-35MHz

DC-Balanced LVDS Deserializer

6

_______________________________________________________________________________________

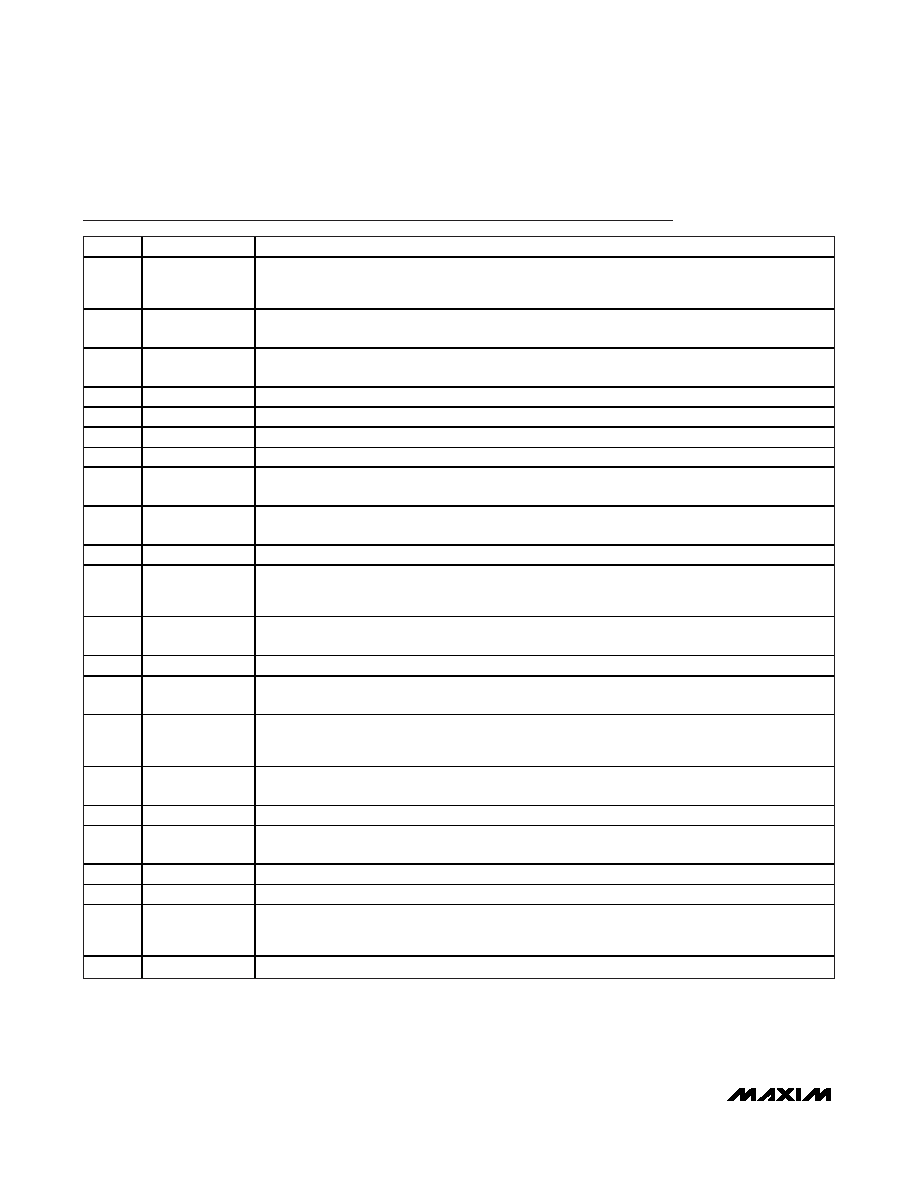

Pin Description

PIN

NAME

FUNCTION

1R/F

Rising or Falling Latch Edge Select. LVTTL/LVCMOS input. Selects the edge of PCLK_OUT for

latching data into the next chip. Set R/F = high for a rising latch edge. Set R/F = low for a falling latch

edge. Internally pulled down to GND.

2

RNG1

LVTTL/LVCMOS Range Select Input. Set to the range that includes the serializer parallel clock input

frequency. Internally pulled down to GND.

3VCCLVDS

LVDS Supply Voltage. Bypass to LVDS GND with 0.1F and 0.001F capacitors in parallel as close

to the device as possible, with the smallest value capacitor closest to the supply pin.

4

IN+

Noninverting LVDS Serial Data Input

5

IN-

Inverting LVDS Serial Data Input

6

LVDS GND

LVDS Supply Ground

7

PLL GND

PLL Supply Ground

8VCCPLL

PLL Supply Voltage. Bypass to PLL GND with 0.1F and 0.001F capacitors in parallel as close to

the device as possible, with the smallest value capacitor closest to the supply pin.

9

RNG0

LVTTL/LVCMOS Range Select Input. Set to the range that includes the serializer parallel clock input

frequency. Internal pulldown to GND.

10

GND

Digital Supply Ground

11

VCC

Digital Supply Voltage. Supply for LVTTL/LVCMOS inputs and digital circuits. Bypass to GND with

0.1F and 0.001F capacitors in parallel as close to the device as possible, with the smallest value

capacitor closest to the supply pin.

12

REFCLK

LVTTL/LVCMOS Reference Clock Input. Apply a reference clock that is within

±2% of the serializer

PCLK_IN frequency. Internally pulled down to GND.

13

PWRDWN

LVTTL/LVCMOS Power-Down Input. Internally pulled down to GND.

14

OUTEN

LVTTL/LVCMOS Output Enable Input. High activates the single-ended outputs. Driving low places

the single-ended outputs in high impedance. Internally pulled down to GND.

15–23

CNTL_OUT [8:0]

LVTTL/LVCMOS Control Data Outputs. CNTL_OUT[8:0] are latched into the next chip on the rising or

falling edge of PCLK_OUT as selected by R/F when DE_OUT is low, and are held at the last state

when DE_OUT is high.

24

DE_OUT

LVTTL/LVCMOS Data Enable Output. High indicates RGB_OUT[17:0] are active. Low indicates

CNTL_OUT[8:0] are active.

25, 37

VCCO GND

Output Supply Ground

26, 38

VCCO

Output Supply Voltage. Bypass to GND with 0.1F and 0.001F capacitors in parallel as close to the

device as possible, with the smallest value capacitor closest to the supply pin.

27

LOCK

LVTTL/LVCMOS Lock Indicator Output. Outputs are valid when LOCK is low.

28

PCLK_OUT

LVTTL/LVCMOS Parallel Clock Output. Latches data into the next chip on the edge selected by R/F.

29–36,

39–48

RGB_OUT [17:0]

LVTTL/LVCMOS Red, Green, and Blue Digital Video Data Outputs. RGB_OUT[17:0] are latched into

the next chip on the edge of PCLK_OUT selected by R/F when DE_OUT is high, and are held at the

last state when DE_OUT is low.

—

EP

Exposed Pad for Thin QFN Package Only. Connect to GND.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| VE-24R-EY-S | CONVERTER MOD DC/DC 7.5V 50W |

| VE-24P-EY-S | CONVERTER MOD DC/DC 13.8V 50W |

| MAX9217EVKIT+ | KIT PCB EVALUATION FOR MAX9217 |

| MAX5393EVKIT+ | KIT EVALUATION FOR MAX5393 |

| 383LX124M016N082 | CAP ALUM 120000UF 16V 20% SNAP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MAX9218EVKIT+ | 功能描述:界面開發(fā)工具 MAX9217/18 Eval Kit RoHS:否 制造商:Bourns 產(chǎn)品:Evaluation Boards 類型:RS-485 工具用于評估:ADM3485E 接口類型:RS-485 工作電源電壓:3.3 V |

| MAX921C/D | 功能描述:校驗器 IC RoHS:否 制造商:STMicroelectronics 產(chǎn)品: 比較器類型: 通道數(shù)量: 輸出類型:Push-Pull 電源電壓-最大:5.5 V 電源電壓-最小:1.1 V 補償電壓(最大值):6 mV 電源電流(最大值):1350 nA 響應(yīng)時間: 最大工作溫度:+ 125 C 安裝風格:SMD/SMT 封裝 / 箱體:SC-70-5 封裝:Reel |

| MAX921C/D DIE | 制造商:Maxim Integrated Products 功能描述: |

| MAX921C/D+ | 功能描述:校驗器 IC RoHS:否 制造商:STMicroelectronics 產(chǎn)品: 比較器類型: 通道數(shù)量: 輸出類型:Push-Pull 電源電壓-最大:5.5 V 電源電壓-最小:1.1 V 補償電壓(最大值):6 mV 電源電流(最大值):1350 nA 響應(yīng)時間: 最大工作溫度:+ 125 C 安裝風格:SMD/SMT 封裝 / 箱體:SC-70-5 封裝:Reel |

| MAX921CPA | 功能描述:校驗器 IC Single Comparator w/1% Precision Ref RoHS:否 制造商:STMicroelectronics 產(chǎn)品: 比較器類型: 通道數(shù)量: 輸出類型:Push-Pull 電源電壓-最大:5.5 V 電源電壓-最小:1.1 V 補償電壓(最大值):6 mV 電源電流(最大值):1350 nA 響應(yīng)時間: 最大工作溫度:+ 125 C 安裝風格:SMD/SMT 封裝 / 箱體:SC-70-5 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。