- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377884 > MB81164442A-125 (Fujitsu Limited) CMOS 4×4M×16 BIT Synchronous Dynamic Random Access Memory (SDRAM)(CMOS 4×4M×16 位同步動(dòng)態(tài)RAM) PDF資料下載

參數(shù)資料

| 型號(hào): | MB81164442A-125 |

| 廠商: | Fujitsu Limited |

| 英文描述: | CMOS 4×4M×16 BIT Synchronous Dynamic Random Access Memory (SDRAM)(CMOS 4×4M×16 位同步動(dòng)態(tài)RAM) |

| 中文描述: | 的CMOS 4 × 4米× 16位同步動(dòng)態(tài)隨機(jī)存取存儲(chǔ)器(SDRAM)(的CMOS 4 × 4米× 16位同步動(dòng)態(tài)RAM)的 |

| 文件頁數(shù): | 17/46頁 |

| 文件大?。?/td> | 642K |

| 代理商: | MB81164442A-125 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁當(dāng)前第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁

17

MB81164442A-125/-100/-84/-67/-125L/-100L/-84L/-67L

DATA INPUT AND OUTPUT (DQ

0

to DQ

3

)

Input data is latched and written into the memory at the clock following the write command input. Data output is

obtained by the following conditions followed by a read command input:

t

RAC

; from the bank active command when t

RCD

(min) is satisfied. (This parameter is reference only.)

t

CAC

; from the read command when t

RCD

is greater than t

RCD

(min).

t

AC

; from the clock edge after t

RAC

and t

CAC

.

The polarity of the output data is identical to that of the input. Data is valid between access time (determined by

the three conditions above) and the next positive clock edge (t

OH

).

DATA I/O MASK (DQM)

DQM is an active high enable input and has an output disable and input mask function. During burst cycle and when

DQM = High is latched by a clock, input is masked at the same clock and output will be masked at the second clock

later while internal burst counter will increment by one or will go to the next stage depending on burst type.

BURST MODE OPERATION AND BURST TYPE

The burst mode provides faster memory access. The burst mode is implemented by keeping the same Row address

and by automatic strobing column address. Access time and cycle time of Burst mode is specified as t

AC

and t

CK

,

respectively. The internal column address counter operation is determined by a mode register which defines burst

type and burst count length of 1, 2, 4 or 8 bits of boundary. In order to terminate or to move from the current burst

mode to the next stage while the remaining burst count is more than 1, the following combinations will be required:

The burst type can be selected either sequential or interleave mode if burst length is 2, 4 or 8. The sequential mode

is an incremental decoding scheme within a boundary address to be determined by count length, it assigns +1 to

the previous (or initial) address until reaching the end of boundary address and then wraps round to least significant

address (= 0). The interleave mode is a scrambled decoding scheme for A

0

and A

2

. If the first access of column

address is even (0), the next address will be odd (1), or vice-versa.

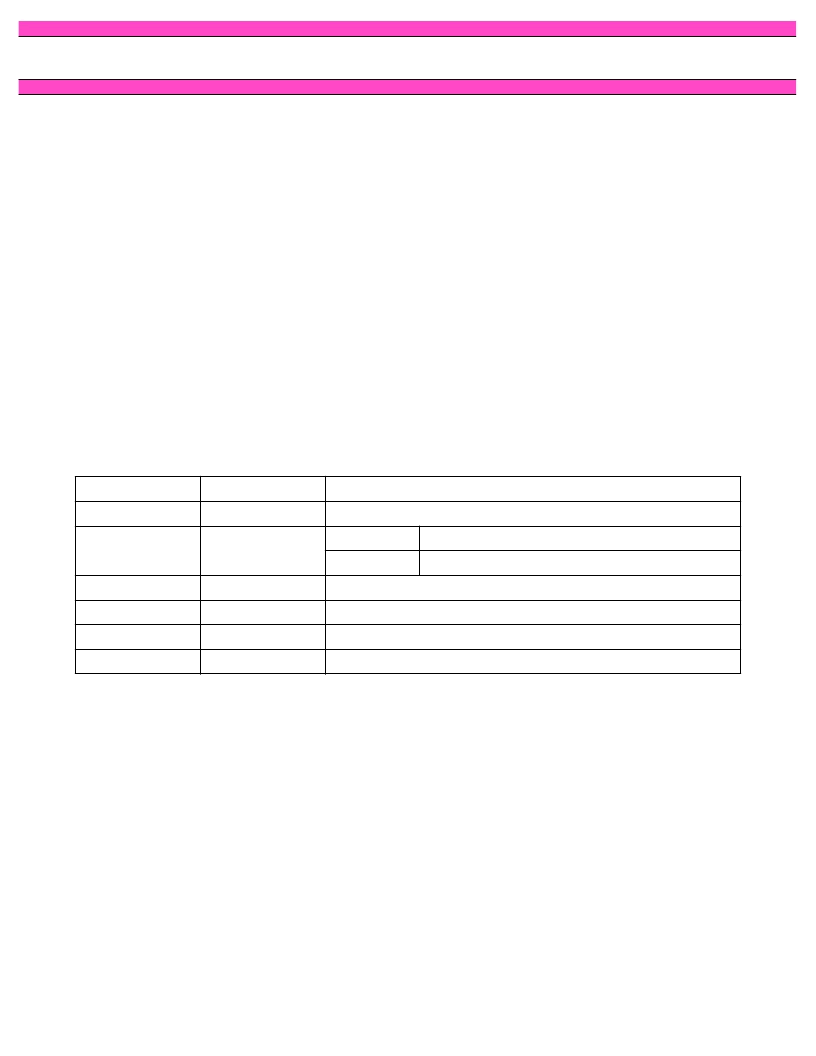

Current Stage

Next Stage

Method (Assert the following command)

Burst Read

Burst Read

Read Command

Burst Read

Burst Write

1st Step

Mask Command (Normally 3 clock cycles)

2nd Step

Write Command after l

OWD

Burst Write

Burst Write

Write Command

Burst Write

Burst Read

Read Command

Burst Read

Precharge

Precharge Command

Burst Write

Precharge

Precharge Command

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MB81164442A-125L | CMOS 4×4M×16 BIT Synchronous Dynamic Random Access Memory (SDRAM)(CMOS 4×4M×16 位同步動(dòng)態(tài)RAM) |

| MB81164442A-67 | CMOS 4×4M×16 BIT Synchronous Dynamic Random Access Memory (SDRAM)(CMOS 4×4M×16 位同步動(dòng)態(tài)RAM) |

| MB81164442A-67L | CMOS 4×4M×16 BIT Synchronous Dynamic Random Access Memory (SDRAM)(CMOS 4×4M×16 位同步動(dòng)態(tài)RAM) |

| MB81164442A-84 | CMOS 4×4M×16 BIT Synchronous Dynamic Random Access Memory (SDRAM)(CMOS 4×4M×16 位同步動(dòng)態(tài)RAM) |

| MB81164442A-84L | CMOS 4×4M×16 BIT Synchronous Dynamic Random Access Memory (SDRAM)(CMOS 4×4M×16 位同步動(dòng)態(tài)RAM) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MB8116E | 制造商:FUJITSU 功能描述: 制造商:FUJITSU 功能描述:8116E |

| MB8117800A-60 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:2 M X 8 BIT FAST PAGE MODE DYNAMIC RAM |

| MB8117800A-70 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:2 M X 8 BIT FAST PAGE MODE DYNAMIC RAM |

| MB812 | 功能描述:ACCY MOUNT BMM 3/4 58A RoHS:是 類別:RF/IF 和 RFID >> RF配件 系列:* 標(biāo)準(zhǔn)包裝:1 系列:* |

| MB812.833 | 功能描述:ACCY MOUNT BMM 3/4 58A RoHS:是 類別:RF/IF 和 RFID >> RF配件 系列:* 標(biāo)準(zhǔn)包裝:1 系列:* |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。