- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377894 > MB86834PFV (FUJITSU LTD) 32-bit Embedded Controller PDF資料下載

參數(shù)資料

| 型號(hào): | MB86834PFV |

| 廠商: | FUJITSU LTD |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 32-bit Embedded Controller |

| 中文描述: | 32-BIT, 108 MHz, RISC MICROCONTROLLER, PQFP176 |

| 封裝: | 24 X 24 MM, PLASTIC, QFP-176 |

| 文件頁數(shù): | 13/82頁 |

| 文件大小: | 1373K |

| 代理商: | MB86834PFV |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁當(dāng)前第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁

MB86830 Series

13

(Continued)

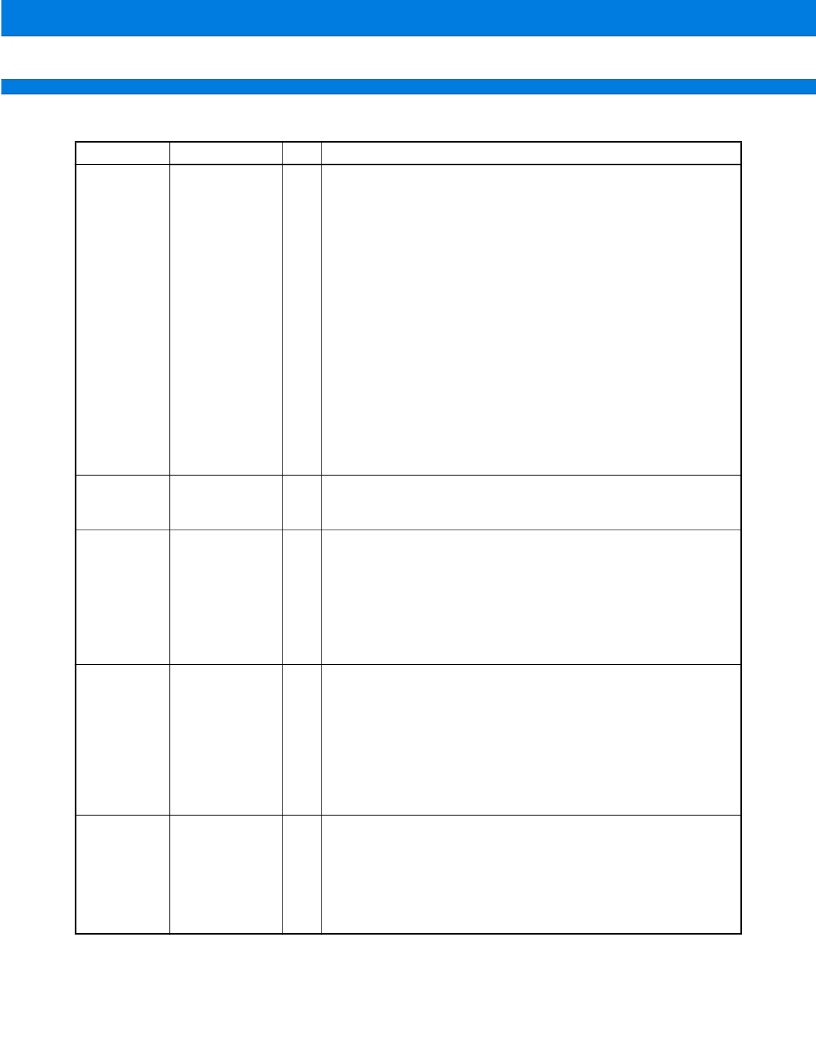

Symbol

(Continued)

Pin name

I/O

Function

BREQ#

BUS REQUEST

I

Bus request signal.

When the BREQ# signal is asserted by external bus mastering, the

CPU releases the bus as shown below upon termination of the current

bus cycle:

(1)When executing the Atomic Load Store instruction, the CPU releas-

es the bus after completing both of loading and storing.

(2)When loading or storing a double word:

If the BREQ# signal is asserted at the first word, the CPU releases

the bus after transfer of the first word. If the BREQ# signal is assert-

ed in the bus cycle for the second word, the CPU releases the bus

after transfer of the second word.

(3)When storing data at the 8/16-bit bus width:

The CPU releases the bus after transfer of that size of data which is

handled by the instruction (for example, after writing 8-bit data four

times when storing word data using an 8-bit bus).

(4)When loading data at the 8/16-bit bus width:

The CPU releases the bus after transfer of one word.

When the ASISEL pin is at the “L” level, the “L” input to the AS# pin

is prohibited in the bus grant state.

BGRNT#

BUS GRANT

O

Bus grant signal.

Upon reception of a bus request (BREQ#), the BGRNT# signal is as-

serted to notify the external device of the bus released status.

IRL3

IRL2

IRL1

IRL0

INTERRUPT RE-

QUEST LEVEL

I

Interrupt input pins.

These pins are used to input an encoded interrupt level. They handle

a group of asynchronous input signals, notifying the IU (integer unit) of

an interrupt level only when the same level is detected twice at the fall

of an external clock pulse. IRL = 0000

2

and IRL = 1111

(2)

indicate no

interrupt and a nonmaskable interrupt as defined in the SPARC archi-

tecture. IRL must be determined for priority by an external circuit and

must be held until confirmed by the CPU.

READY#

EXTERNAL

READY

I

Ready signal input pin.

Input the “L” level signal to upon completion of a bus cycle.

Upon reception of READY#=“L”, the CPU starts the next bus cycle.

Note, however, that the“L” input to this pin is not necessary when the

internal wait state generator circuit is used.

For burst transfer, instruction fetch or data load using an 8-bit bus, in-

struction fetch or data load using an 16-bit bus, the pin must input the

ready signal for the prescribed number of times whenever the address

strobe signal is asserted.

MEXC#

MEMORY

EXCEPTION

I

Memory access exception pin.

If this pin inputs the “L” level signal in the same cycle as the ready sig-

nal input, the CPU handles it as an instruction access or data access

exception to generate a trap. The operation of the device is unpredict-

able if the MEXC# signal is asserted at a timing other than the same

cycle as the ready signal input. (An exception occurring with the PSR

ET bit set to “0” results in an error state.)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MB86835 | 32-bit Embedded Controller |

| MB86835PMT2 | 32-bit Embedded Controller |

| MB86836 | 32-bit Embedded Controller |

| MB86836-108PBT | 32-bit Embedded Controller |

| MB86836PBT | 32-bit Embedded Controller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MB86835 | 制造商:FUJITSU 制造商全稱:Fujitsu Component Limited. 功能描述:32-bit Embedded Controller |

| MB86835PMT2 | 制造商:FUJITSU 制造商全稱:Fujitsu Component Limited. 功能描述:32-bit Embedded Controller |

| MB86836 | 制造商:FUJITSU 制造商全稱:Fujitsu Component Limited. 功能描述:32-bit Embedded Controller |

| MB86836-108PBT | 制造商:FUJITSU 制造商全稱:Fujitsu Component Limited. 功能描述:32-bit Embedded Controller |

| MB86836-108PMT2 | 制造商:FUJITSU 制造商全稱:Fujitsu Component Limited. 功能描述:32-bit Embedded Controller |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。